C28x Hardware Interrupt

C28x 处理器上处理硬件中断的中断服务程序

库:

C2000 Microcontroller Blockset /

Scheduling

描述

基于定时器中断的执行调度模型无法满足某些实时应用对响应外部事件的要求。C28x Hardware Interrupt 模块通过允许异步处理由 C28x DSP 芯片支持库中其他模块管理的事件所触发的中断,解决了这一问题。

当 C28x Hardware Interrupt 模块启用外部中断选择功能时,该选择将激活所选通用 I/O 引脚的中断功能。要配置这些引脚,请参阅配置参数 > 硬件实现 > Hardware board settings > Target hardware resources > External Interrupt窗格。有关更多信息,请参阅Model Configuration Parameters for Texas Instruments C2000 Processors。

任务优先级表示与异步中断相关联的任务的相对重要性。该字段中的最低值代表最高优先级。基础速率任务的默认优先级值为 40,因此每个异步触发任务的优先级值必须小于 40(以配置为更高优先级),这些任务才能抢占基础速率任务。

抢占标志位决定了给定中断是否可被抢占。抢占机制优先于优先级机制。若中断触发了更高优先级的任务,而较低优先级的任务正在运行,则较低优先级任务的执行可被暂停,并在较高优先级任务完成后恢复。前提是该较低优先级任务已被配置为可抢占。

向量化输出

该模块的输出是一个函数调用。函数调用行的长度等于该模块设置为处理的中断数量.每个中断由模块对话框中显示的四个参数表示。这些参数是一组四个等长向量。每个中断由每个参数中的一个元素表示(共四个元素),这些向量中相同位置的元素各取一个。

每个中断由以下内容描述:

CPU 中断编号

外围中断扩展 (PIE) 中断编号

任务优先级

抢占标志

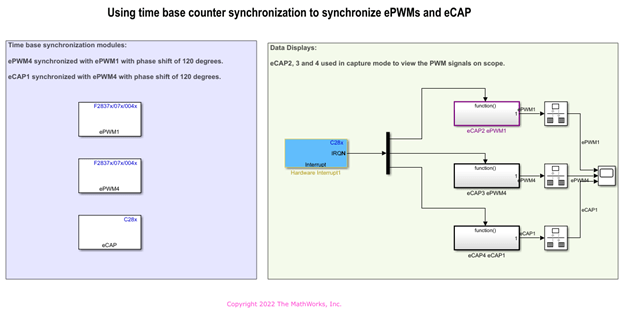

示例

利用 ADC 中断实现 ADC-PWM 同步

本示例展示了如何使用 ADC 模块对模拟电压进行采样,以及如何使用 PWM 模块生成脉冲波形。本示例还展示了如何使用 Hardware Interrupt 模块将 PWM 占空比的变化与电压的模数转换同步。在生成的代码中,ADC 输入电压的变化会改变 PWM 输出的占空比。PWM 波形的周期保持不变。

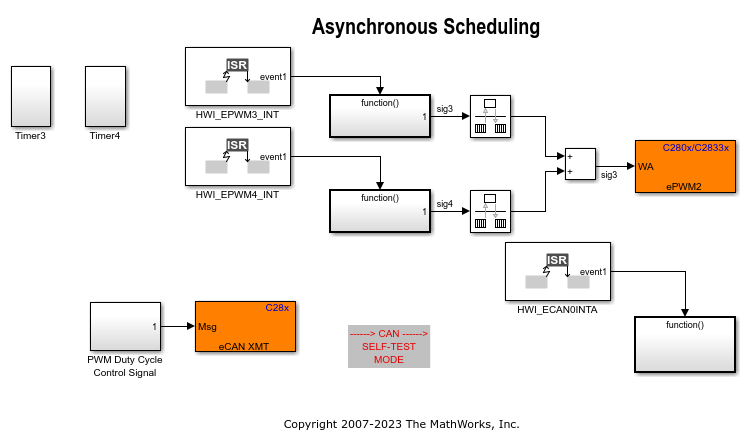

异步调度

本示例展示了如何使用 Texas Instruments™ C28x™ 外设和 Hardware Interrupt 模块以异步方式控制 Simulink® 函数调用子系统的实时执行。

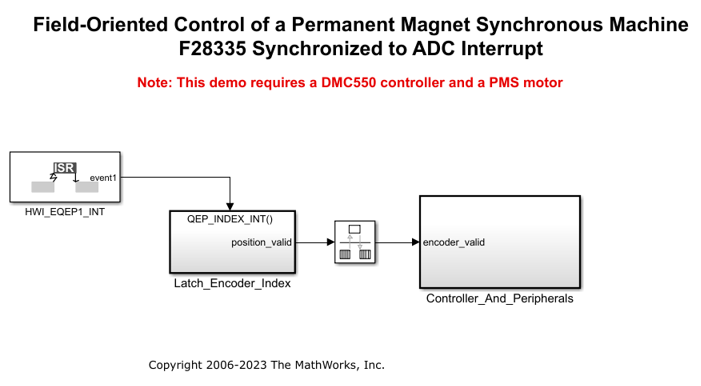

基于 C2000 处理器的正交编码器永磁同步电机磁场定向控制

本例采用磁场定向控制 (FOC) 技术来控制三相永磁同步电机 (PMSM) 的速度。FOC 算法需要转子位置反馈,该反馈由正交编码器传感器获得。有关 FOC 的详细信息,请参阅磁场定向控制 (FOC) (Motor Control Blockset)。

使用 Solar Explorer 套件的带 MPPT 功能的光伏逆变器

本示例展示了如何使用 C2000™ Microcontroller Blockset 实现光伏 (PV) 逆变器系统。该示例使用 Texas Instruments太阳能探索套件以及 Texas Instruments F28035 控制卡。

端口

输入

中断模块在您启用 SimIRQ 输入端口时,会在仿真中发起函数调用。然而,在生成的代码中,SimIRQ 被忽略了。

依赖关系

要启用 SimIRQ 端口,请选择启用仿真端口参数。

数据类型: Boolean

输出

该模块的输出是一个函数调用。函数调用行的长度等于该模块设置为处理的中断数量.

参数

输入一个包含 CPU 中断编号的向量,用于处理您希望异步处理的中断。

输入一个包含 PIE 中断编号的向量,用于处理您希望异步处理的中断。

输入一个任务优先级向量,用于指定要异步处理的中断。

任务优先级表示与异步中断相关联的任务的相对重要性。该字段中的最低值代表最高优先级。基础速率任务的默认优先级值为 40,因此每个异步触发任务的优先级值必须小于 40(以配置为更高优先级),这些任务才能抢占基础速率任务。

输入一个向量,其中包含用于异步处理中断的抢占标志。

抢占标志位决定了给定中断是否可被抢占。抢占机制优先于优先级机制。若中断触发了更高优先级的任务,而较低优先级的任务正在运行,则较低优先级任务的执行可被暂停,并在较高优先级任务完成后恢复。前提是该较低优先级任务已被配置为可抢占。

选择此参数可添加兼容的仿真输入端口。

选择此参数可使您在 Simulink® 软件模型的上下文中测试异步中断处理。

PIE 和 CPU 中断编号

每个中断由 CPU 中断号、PIE 中断号、任务优先级和抢占标志描述。

CPU 和 PIE 中断编号共同唯一地指定了单个外设或外设模块的单个中断。

支持 12×8 中断的 c28x 处理器 F280013x 和 F280015x 的 PIE 和 CPU 中断编号如下:

F280013x 和 F280015x 处理器的 PIE 和 CPU 中断编号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | ADCA1 | ADCC1 | - | XINT1 | XINT2 | SYS_ERR | TIMER0 | WAKE |

| 2 | EPWM1_TZ | EPWM2_TZ | EPWM3_TZ | EPWM4_TZ | EPWM5_TZ | EPWM6_ TZ | EPWM7_TZ | |

| 3 | EPWM1 | EPWM2 | EPWM3 | EPWM4 | EPWM5 | EPWM6 | EPWM7 | |

| 4 | ECAP1 | ECAP2 | - | - | - | - | - | |

| 5 | EQEP1 | - | - | - | - | - | - | |

| 6 | SPIA_RX | SPIA_TX | - | - | - | - | DCC0 | |

| 7 | - | - | - | - | - | - | - | - |

| 8 | I2CA | I2CA_FIFO | I2CB | I2CB_FIFO | SCIC_RX | SCIC_TX | - | - |

| 9 | SCIA_RX | SCIA_TX | SCIB_RX | SCIB_TX | CANA_0 | CANA_1 | - | - |

| 10 | ADCA_EVT | ADCA2 | ADCA3 | ADCA4 | ADCC_EVT | ADCC2 | ADCC3 | ADCC4 |

| 11 | - | - | - | - | - | - | - | - |

| 12 | XINT3 | XINT4 | XINT5 | - | FLSS_INT | - | - | - |

支持 12×16 中断的 TI 处理器 F28P65x 的 PIE 和 CPU 中断编号如下:

F28P65x 系列微控制器的外围设备中断号与 CPU 中断号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | ADCA1 | ADCB1 | ADCC1 | XINT1 | XINT2 | - | 定时器 0 | WAKE / WDOG |

| 2 | EPWM1_TZ | EPWM2_TZ | EPWM3_TZ | EPWM4_TZ | EPWM5_TZ | EPWM6_ TZ | EPWM7_TZ | EPWM8_TZ |

| 3 | EPWM1 | EPWM2 | EPWM3 | EPWM4 | EPWM5 | EPWM6 | EPWM7 | EPWM8 |

| 4 | ECAP1 | ECAP2 | ECAP3 | ECAP4 | ECAP5 | ECAP6 | ECAP7 | 保留 |

| 5 | EQEP1 | EQEP2 | EQEP3 | EQEP4 | CLB1 | CLB2 | CLB3 | CLB4 |

| 6 | SPIA_RX | SPIA_TX | SPIB_RX | SPIB_TX | LINA_0 | LINA_1 | LINB_0 | LINB_1 |

| 7 | DMA_CH1 | DMA_CH2 | DMA_CH3 | DMA_CH4 | DMA_CH5 | DMA_CH6 | EQEP_5 | EQEP_6 |

| 8 | I2CA | I2CA_FIFO | I2CB | I2CB_FIFO | UARTA_INT | UARTB_INT | EPWM17_TZ | EPWM18_TZ |

| 9 | SCIA_RX | SCIA_TX | SCIB_RX | SCIB_TX | DCANA_1 | DCANA_2 | EPWM17 | EPWM18 |

| 10 | ADCA_EVT | ADCA2 | ADCA3 | ADCA4 | ADCB_EVT | ADCB2 | ADCB3 | ADCB4 |

| 11 | CPU1_CLA1_1 | CPU1_CLA1_2 | CPU1_CLA1_3 | CPU1_CLA1_4 | CPU1_CLA1_5 | CPU1_CLA1_6 | CPU1_CLA1_7 | CPU1_CLA1_8 |

| 12 | XINT3 | XINT4 | XINT5 | CPU1_MPOST_INT | FLSS_INT | - | FPU_OVERFLOW | FPU_UNDERFLOW |

| PIE ⇒ | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | I2CA | SYS_ERR | ECATSYNC0 | ECATINTn | CIPC0 | CIPC1 | CIPC2 | CIPC3 |

| 2 | EPWM9_TZ | EPWM10_ TZ | EPWM11_TZ | EPWM12_TZ | EPWM13_TZ | EPWM14_TZ | EPWM15_TZ | EPWM16_TZ |

| 3 | EPWM9 | EPWM10 | EPWM11 | EPWM12 | EPWM13 | EPWM14 | EPWM15 | EPWM16 |

| 4 | FSITXA_INT1 | FSITXA_INT2 | FSITXB_INT1 | FSITXB_INT2 | FSIRXA_INT1 | FSIRXA_INT2 | FSIRXB_INT1 | FSIRXB_INT2 |

| 5 | SDFM1 | SDFM2 | ECATRST | ECATSYNC1 | SDFM1DR1 | SDFM1DR2 | SDFM1DR3 | SDFM1DR4 |

| 6 | SPIC_RX | SPIC_TX | SPID_RX | SPID_TX | SDFM2DR1 | SDFM2DR2 | SDFM2DR3 | SDFM2DR4 |

| 7 | FSITXA_INT1 | FSITXA_INT2 | FSIRXA_INT1 | FSIRXA_INT2 | SDFM3DR1 | SDFM3DR2 | SDFM3DR3 | SDFM3DR4 |

| 8 | - | - | SDFM3 | SDFM4 | CLB5 | CLB6 | - | - |

| 9 | MCANSS_A0 | MCANSS_A1 | MCANSS_ECC_CORR_PLS | MCANSS_WAKE_AND_TS_PLS | PMBUSA | AES_INT | USBA | 保留 |

| 10 | ADCC_EVT | ADCC2 | ADCC3 | ADCC4 | 保留 | 保留 | 保留 | ADCHECKINT |

| 11 | MCANSS_B0 | MCANSS_B1 | MCANSS_BECC_CORR_PLS | MCANSS_B_WAKE_AND_TS_PLS | SDFM4DR1 | SDFM4DR2 | SDFM4DR3 | SDFM4DR4 |

| 12 | _ | ECAP6_INT2 | ECAP7_INT2 | - | CPU1_CRC_INT | CPU1_CLA1CRC_INT | CPU1_CLA OVER FLOW | CPU1_CLA UNDERFLOW |

支持 12×16 中断的 TI 处理器 F28P55x 的 PIE 和 CPU 中断编号如下:

F28P55x 系列微控制器中的 PIE 和 CPU 中断编号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | ADCA1 | ADCB1 | ADCC1 | XINT1 | XINT2 | SYS_ERR | 定时器 0 | WAKE / WDOG |

| 2 | EPWM1_TZ | EPWM2_TZ | EPWM3_TZ | EPWM4_TZ | EPWM5_TZ | EPWM6_ TZ | EPWM7_TZ | EPWM8_TZ |

| 3 | EPWM1 | EPWM2 | EPWM3 | EPWM4 | EPWM5 | EPWM6 | EPWM7 | EPWM8 |

| 4 | ECAP1 | ECAP2 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 5 | EQEP1 | EQEP2 | EQEP3 | 保留 | CLB1 | CLB2 | 保留 | 保留 |

| 6 | SPIA_RX | SPIA_TX | SPIB_RX | SPIB_TX | 保留 | 保留 | DCC0 | DCC1 |

| 7 | DMA_CH1 | DMA_CH2 | DMA_CH3 | DMA_CH4 | DMA_CH5 | DMA_CH6 | PMBUSA | 保留 |

| 8 | I2CA | I2CA_FIFO | I2CB | I2CB_FIFO | SCIC_RX | SCIC_TX | 保留 | 保留 |

| 9 | SCIA_RX | SCIA_TX | SCIB_RX | SCIB_TX | 保留 | 保留 | MCANASS0 | MCANASS1 |

| 10 | ADCA_EVT | ADCA2 | ADCA3 | ADCA4 | ADCB_EVT | ADCB2 | ADCB3 | ADCB4 |

| 11 | CLA1_1 | CLA1_2 | CLA1_3 | CLA1_4 | CLA1_5 | CLA1_6 | CLA1_7 | CLA1_8 |

| 12 | XINT3 | XINT4 | XINT5 | 保留 | FLSS_INT | 保留 | MCANASS_WAKE_AND_TS_PLS | MCANASS_ECC_CORR_PLS |

| PIE ⇒ | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | ADCD1 | ADCE1 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 2 | EPWM9_TZ | EPWM10_ TZ | EPWM11_TZ | EPWM12_TZ | 保留 | 保留 | 保留 | 保留 |

| 3 | EPWM9 | EPWM10 | EPWM11 | EPWM12 | 保留 | 保留 | 保留 | 保留 |

| 4 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 5 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 6 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 7 | 保留 | 保留 | FSITXA_INT1 | FSITXA_INT2 | FSIRXA_INT1 | FSIRXA_INT2 | 保留 | 保留 |

| 8 | LINA_0 | LINA_1 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 9 | MCANBSS0 | MCANBSS1 | MCANBSS_ECC_CORR_PLS | MCANSS_WAKE_AND_TS_PLS | 保留 | 保留 | USB | NPU |

| 10 | ADCC_EVT | ADCC2 | ADCC3 | ADCC4 | ADCD_EVT | ADCD2 | ADCD3 | ADCD4 |

| 11 | ADCE_EVT | ADCE2 | ADCE3 | ADCE4 | 保留 | 保留 | 保留 | 保留 |

| 12 | _ | ECAP6_INT2 | ECAP7_INT2 | - | CPU1_CRC_INT | CPU1_CLA1CRC_INT | CPU1_CLA OVER FLOW | CPU1_CLA UNDERFLOW |

下表列出了支持 12×8 中断的 c28x 系列处理器(包括 F280x、F2802x、F2803x、F2805x、F2806x、F2833x、F28M35x 和 F28M36x)的 PIE 和 CPU 中断编号。行标题 1–12 代表 CPU 值,列标题 1–8 代表 PIE 值。

F280x、F2802x、F2803x、F2805x、F2806x、F2833x、F28M35x 和 F28M36x 处理器的 PIE 和 CPU 中断编号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | SEQ1INT (ADC) / ADCINT1 | SEQ2INT (ADC) / ADCINT2 | 保留 | XINT1 | XINT2 | ADCINT / ADCINT9 | TINT0(定时器 0) | WAKEINT (LPM/WD) |

| 2 | EPWM1_TZINT | EPWM2_TZINT | EPWM3_TZINT | EPWM4_TZINT | EPWM5_TZINT | EPWM6_ TZINT | EPWM7_TZINT | EPWM8_TZINT |

| 3 | EPWM1_INT | EPWM2_INT | EPWM3_INT | EPWM4_INT | EPWM5_INT | EPWM6_ INT | EPWM7_INT | EPWM8_INT |

| 4 | ECAP1_INT | ECAP2_INT | ECAP3_INT | ECAP4_INT | ECAP5_INT | ECAP6_INT | EPWM10_TZINT / HRCAP1_INT | EPWM9_TZINT / HRCAP2_INT |

| 5 | EQEP1_INT | EQEP2_INT | EQEP3_INT | HRCAP3_INT | HRCAP4_INT | 保留 | EPWM10_INT | EPWM9_INT |

| 6 | SPIRXINTA (SPI-A) | SPITXINTA (SPI-A) | SPIRXINTB(SPIB_RX)/ MRINTB(McBSP-B) | SPITXINTB (SPIB_TX) / MXINTB (McBSP-B) | SPIRXINTC (SPI-C) / MRINTA (McBSP-A_RX) | SPITXINTC (SPI-C) / MXINTA (McBSP-A_TX) | SPIRXINTD (SPI-D) / EPWM12_TZINT | SPITXINTD (SPI-D) / EPWM11_TZINT |

| 7 | DINTCH1 (DMA1) | DINTCH2 (DMA2) | DINTCH3 (DMA3) | DINTCH4 (DMA4) | DINTCH5 (DMA5) | DINTCH6 (DMA6) | EPWM12_INT | EPWM11_INT |

| 8 | I2CINT1A | I2CINT2A | 保留 | 保留 | SCIRXINTC (SCI-C) | SCITXINTC (SCI-C) | 保留 | 保留 |

| 9 | SCIRXINTA (SCIA_RX) | SCITXINTA (SCIA_TX) | SCIRXINTB (SCIB_RX) / LINA_INT0 | SCITXINTB (SCIB_TX) / LINA_INT1 | ECAN0INTA (CANA_1) | ECAN1INTA (CANA_2) | ECAN0INTB (CANB_1) | ECAN1INTB (CANB_2) |

| 10 | EPWM9_TZINT / ADCINT1 | EPWM10_TZINT / ADCINT2 | EPWM11_TZINT / ADCINT3 | EPWM12_TZINT / ADCINT4 | EPWM13_TZINT / ADCINT5 | EPWM14_TZINT / ADCINT6 | EPWM15_TZINT / ADCINT7 | EPWM16_TZINT / ADCINT8 |

| 11 | CLA1_INT1 / EPWM9_INT7 / MTOCIPCINT1 | CLA1_INT2 / EPWM10_INT / MTOCIPCINT2 | CLA1_INT3 / EPWM11_INT / MTOCIPCINT3 | CLA1_INT4 / EPWM12_INT / MTOCIPCINT4 / | CLA1_INT5 / EPWM13_INT | CLA1_INT6 / EPWM14_INT | CLA1_INT7 / EPWM15_INT | CLA1_INT8 / EPWM16_INT |

| 12 | XINT3 | XINT4 / C28FLSINGERR | XINT5 | XINT6 / C28RAMSINGERR | XINT7 / C28RAMACCVIOL | 保留 | LVF | LUF |

支持 12×16 中断的 c28x 系列处理器(F2807x、F2837xS、F2837xD、F2838x、F28004x、F28002x 和 F28003x)的 PIE 和 CPU 中断编号如下:

F2807x、F2837xS、F2837xD、F2838x、F28004x、F28002x 和 F28003x 处理器的 PIE 和 CPU 中断编号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | ADCA1 | ADCB1 | ADCC1 | XINT1 | XINT2 | ADCD1 | 定时器 0 | WAKE / WDOG |

| 2 | EPWM1_TZ | EPWM2_TZ | EPWM3_TZ | EPWM4_TZ | EPWM5_TZ | EPWM6_ TZ | EPWM7_TZ | EPWM8_TZ |

| 3 | EPWM1 | EPWM2 | EPWM3 | EPWM4 | EPWM5 | EPWM6 | EPWM7 | EPWM8 |

| 4 | ECAP1 | ECAP2 | ECAP3 | ECAP4 | ECAP5 | ECAP6 | ECAP7 | 保留 |

| 5 | EQEP1 | EQEP2 | EQEP3 | 保留 | CLB1 | CLB2 | CLB3 | CLB4 |

| 6 | SPIA_RX | SPIA_TX | SPIB_RX | SPIB_TX | MCBSPA_RX | MCBSPA_TX | MCBSPB_RX | MCBSPB_TX |

| 7 | DMA_CH1 | DMA_CH2 | DMA_CH3 | DMA_CH4 | DMA_CH5 | DMA_CH6 | 保留 | 保留 |

| 8 | I2CA | I2CA_FIFO | I2CB | I2CB_FIFO | SCIC_RX | SCIC_TX | SCID_RX | SCID_TX |

| 9 | SCIA_RX | SCIA_TX | SCIB_RX | SCIB_TX | CANA_0 | CANA_1 | CANB_0 | CANB_1 |

| 10 | ADCA_EVT | ADCA2 | ADCA3 | ADCA4 | ADCB_EVT | ADCB2 | ADCB3 | ADCB4 |

| 11 | CLA1_1 | CLA1_2 | CLA1_3 | CLA1_4 | CLA1_5 | CLA1_6 | CLA1_7 | CLA1_8 |

| 12 | XINT3 | XINT4 | XINT5 | MPOST | FMC.DONE | VCU | FPU_OVERFLOW | FPU_UNDERFLOW |

| PIE ⇒ | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | I2CA | SYS_ERR | ECATSYNC0(仅限 CPU1) | ECATINTn(仅限 CPU1) | IPC0/CIPC0 | IPC1/CIPC1 | IPC2/CIPC2 | IPC3/CIPC3 |

| 2 | EPWM9_TZ | EPWM10_ TZ | EPWM11_TZ | EPWM12_TZ | EPWM13_TZ | EPWM14_TZ | EPWM15_TZ | EPWM16_TZ |

| 3 | EPWM9 | EPWM10 | EPWM11 | EPWM12 | EPWM13 | EPWM14 | EPWM15 | EPWM16 |

| 4 | FSITXA_INT1 | FSITXA_INT2 | FSITXB_INT1 | FSITXB_INT2 | FSIRXA_INT1 | FSIRXA_INT2 | FSIRXB_INT1 | FSIRXB_INT2 |

| 5 | SD1 / SDFM1 | SD2/SDFM1 | ECATRSTINTn(仅限 CPU1) | ECATSYNC1(仅限 CPU1) | SDFM1DR1 | SDFM1DR2 | SDFM1DR3 | SDFM1DR4 |

| 6 | SPIC_RX | SPIC_TX | SPID_RX | SPID_TX | SDFM2DR1 | SDFM2DR2 | SDFM2DR3 | SDFM2DR4 |

| 7 | FSIRXC_INT1 | FSIRXC_INT2 | FSIRXD_INT1 | FSIRXD_INT2 | FSIRXE_INT1 | FSIRXE_INT2 | FSIRXF_INT1 | FSIRXF_INT2 |

| 8 | LINA_0/FSIRXG_INT1 | LINA_1/FSIRXG_INT2 | FSIRXH_INT1 | FSIRXH_INT2 | PMBUSA/CLB5 | CLB6 | UPPA(仅限 CPU1)/CLB7 | CLB8 |

| 9 | MCANSS_INT0(仅限 CPU1) | MCANSS_INT1(仅限 CPU1) | MCANSS_ECC_CORR_PUL_INT(仅限 CPU1) | MCANSS_WAKE_AND_TS_PLS_INT(仅限 CPU1) | PMBUSA | CM_STATUS(仅限 CPU1) | USBA(仅限 CPU1) | 保留 |

| 10 | ADCC_EVT | ADCC2 | ADCC3 | ADCC4 | ADCD_EVT | ADCD2 | ADCD3 | ADCD4 |

| 11 | CMTOCPUxIPCINTR0 | CMTOCPUxIPCINTR1 | CMTOCPUxIPCINTR2 | CMTOCPUxIPCINTR3 | CMTOCPUxIPCINTR4 | CMTOCPUxIPCINTR5 | CMTOCPUxIPCINTR6 | CMTOCPUxIPCINTR7 |

| 12 | EMIF_ ERROR | RAM_CORRECTABLE_ERROR/ECAP6INT2 | 可纠错闪存错误/ECAP7INT2 | RAM_ACCESS_VIOLATION | SYS_PLL_ SLIP/CPUxCRC_INT | AUX_PLL_SLIP//CLA1CRC_INT | CLA OVER FLOW | CLA UNDERFLOW |

c281x 处理器的 PIE 和 CPU 中断号如下:

C281x 处理器的 PIE 和 CPU 中断编号

| PIE ⇒ | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| CPU ⇓ | ||||||||

| 1 | PDPINTA (EV-A) | PDPINTB (EV-B) | 保留 | XINT1 | XINT2 | ADCINT (ADC) | TINT0(定时器 0) | WAKEINT (LPM/WD) |

| 2 | CMP1INT (EV-A) | CMP2INT (EV-A) | CMP3INT (EV-A) | T1PINT (EV-A) | T1CINT (EV-A) | T1UFINT (EV-A) | T1OFINT (EV-A) | 保留 |

| 3 | T2PINT (EV-A) | T2CINT (EV-A) | T2UFINT (EV-A) | T2OFINT (EV-A) | CAPINT1 (EV-A) | CAPINT2 (EV-A) | CAPINT3 (EV-A) | 保留 |

| 4 | CMP4INT (EV-B) | CMP5INT (EV-B) | CMP6INT (EV-B) | T3PINT (EV-B) | T3CINT (EV-B) | T3UFINT (EV-B) | T3OFINT (EV-B) | 保留 |

| 5 | T4PINT (EV-B) | T4CINT (EV-B) | T4UFINT (EV-B) | T4OFINT (EV-B) | CAPINT4 (EV-B) | CAPINT5 (EV-B) | CAPINT6 (EV-B) | 保留 |

| 6 | SPIRXINTA (SPI) | SPITXINTA (SPI) | 保留 | 保留 | MRINT (McBSP) | MXINT (McBSP) | 保留 | 保留 |

| 7 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 8 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 9 | SCIRXINTA (SCI-A) | SCITXINTA (SCI-A) | SCIRXINTB (SCI-B) | SCITXINTB (SCI-B) | ECAN0INT (CAN) | ECAN1INT (CAN) | 保留 | 保留 |

| 10 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 11 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

| 12 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 | 保留 |

版本历史记录

在 R2016b 中推出

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)