直流-直流功率转换中的控制律加速器

本示例展示了如何使用控制律加速器 (CLA) 管理闭环 DC-DC 电源转换系统的电压模式控制 (VMC) 算法。辅助软件电流保护回路由 C2000 CPU 管理。在 TMS320F28379D 和类似的处理器系列中,CLA 执行算法的硬实时部分,可以与 ADC 和 PWM 等硬件外设连接。C2000 CPU 更适合算法中需要多任务处理、异步事件处理以及与其他核心通信的硬实时部分。虽然此示例扩展了 基于 MCU 的 C2000 DC-DC 降压转换器 示例中开发的 DC-DC 降压转换器,但所提出的策略可以应用于任何设计,其中资源密集型硬实时进程在 CLA 上执行,而实时多任务进程在 C2000 CPU 上运行。

所需硬件

TI Delfino F28379D LaunchPad 或 F28P650D LaunchPad(需要 LaunchPad 型直通插座条连接器,如附录 9.1 中所述)

可用模型

TI Delfino F28379D LaunchPad:

CPU1 模型:soc_dcdc_pwr_conv_c28x_ref.slx

TI F28P650D LaunchPad:

硬件连接

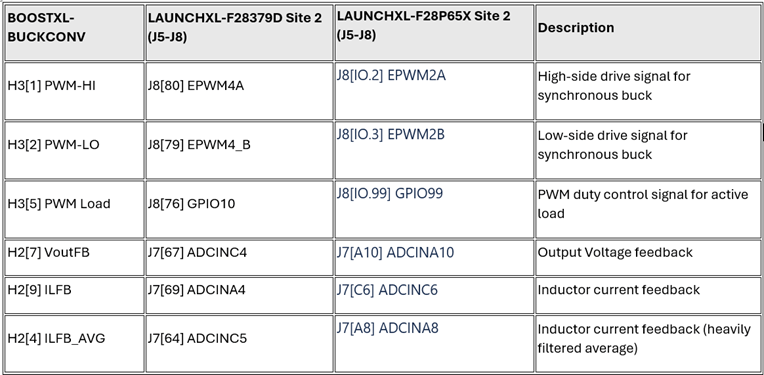

按照下表中的详细说明,将数字电源降压转换器 BoosterPack (BOOSTXL-BUCKCONV) 连接到 Texas Instruments Delfino F28379D LaunchPad 或 Texas Instruments F28P650D LaunchPad。

CLA 上的电压模式控制算法

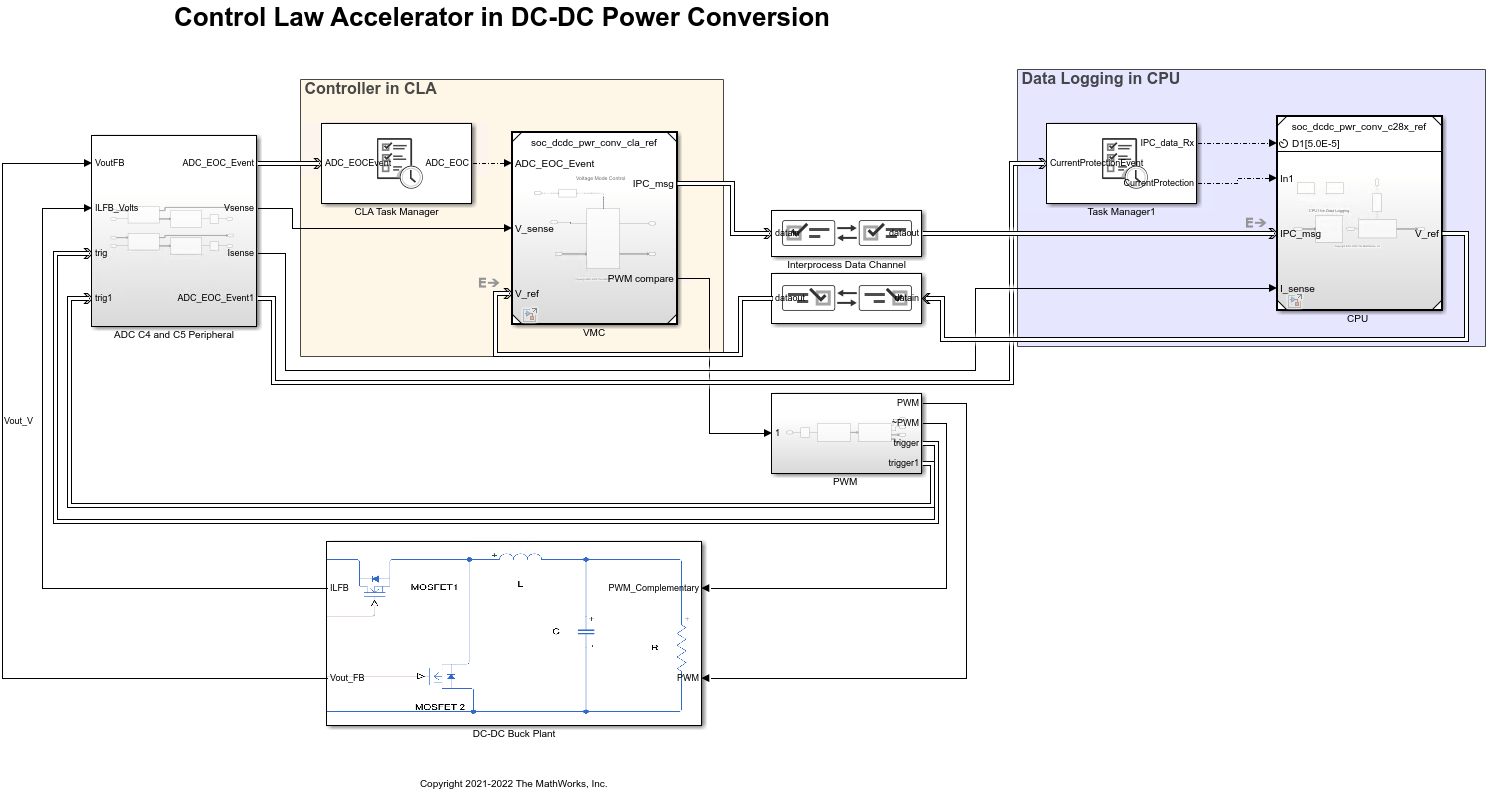

该模型展示了在 CLA 上执行电压模式控制 (VMC) 算法的 DC-DC 电源转换系统。该模型为 CLA 和 C2000 CPU 参考模型分配了一个单独的 Task Manager (SoC Blockset) 模块。有关 CLA 上任务调度的更多信息,请参阅 CLA 任务管理器文档。打开模型。

open_system('soc_dcdc_pwr_conv');

顶级模型 soc_dcdc_pwr_conv 不会通过向 none 添加处理单元参数来构建。在每个参考模型中,将处理单元参数设置为特定的处理器。在 System on Chip 选项卡上,点击硬件设置以打开配置参数窗口。

对于 CLA 参考模型,请在硬件实现选项卡中将 Processing Unit 设置为

CPU1CLA1。对于 C2000 CPU 参考型号,请在硬件实现选项卡中将 Processing Unit 设置为

c28xCPU1。

在任务映射器工具中为 CLA 选择合适的中断源。本例使用 ADCCINT4 作为 CLA 的 ADC 中断。有关 VMC 设计和外围设备配置的更多信息,请参阅 基于 MCU 的 C2000 DC-DC 降压转换器。

CLA 限制了对区域记忆的访问。使用 CLA 参考模型中的 代码映射编辑器 - C (Embedded Coder) 工具指定输入端口、输出端口、信号、状态和内部数据的内存部分。您可以通过指定 initialize、execute 和 terminate 函数程序空间来确保 CLA 对这些部分具有适当的访问权限。默认情况下,该模型具有适用于 CLA 的代码映射。

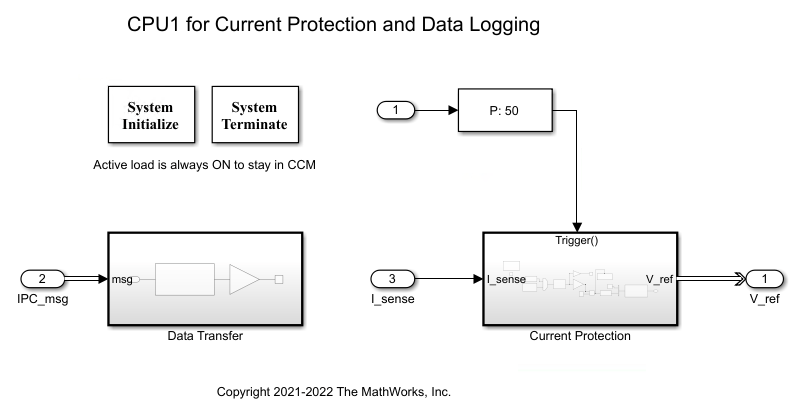

C2000 CPU 的电流保护算法

当前保护算法运行在 C2000 CPU 上。该算法监控电流水平,并在电流峰值超过设定的电流阈值时保护硬件。CLA 和 C2000 CPU 可以访问相同的外围模块。该算法是功率转换系统的辅助异步组件,是 CLA 上计算量更大的 VMC 算法。

C2000 CPU 将电压参考信号发送到 CLA,并接收和记录电流和电压反馈值。Interprocess Data Channel (SoC Blockset)模块模拟 CLA 和 C2000 CPU 之间的数据交换。当部署到硬件时,这些模块利用共享内存的一部分在 CLA 和 C2000 CPU 之间进行数据传输,并确保数据完整性。

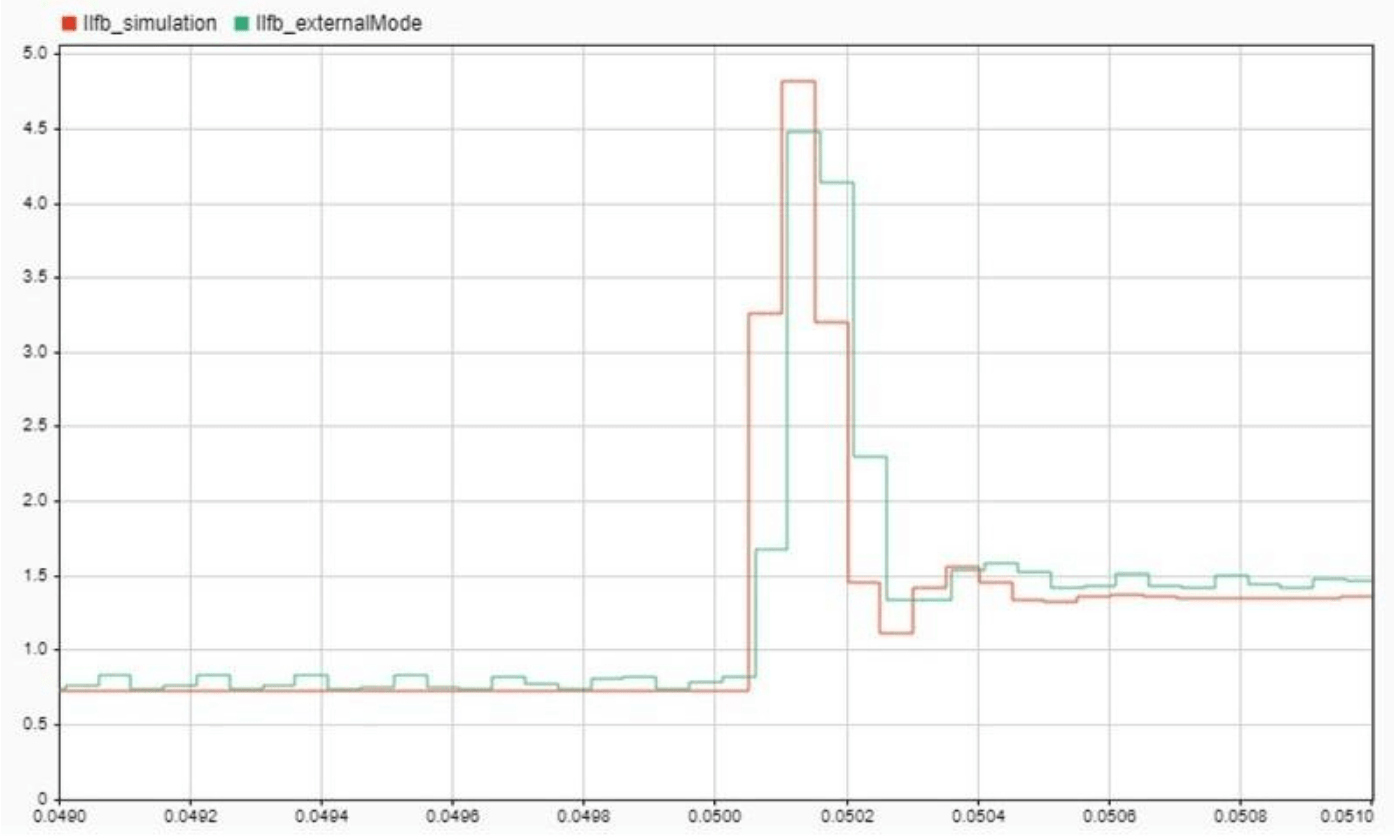

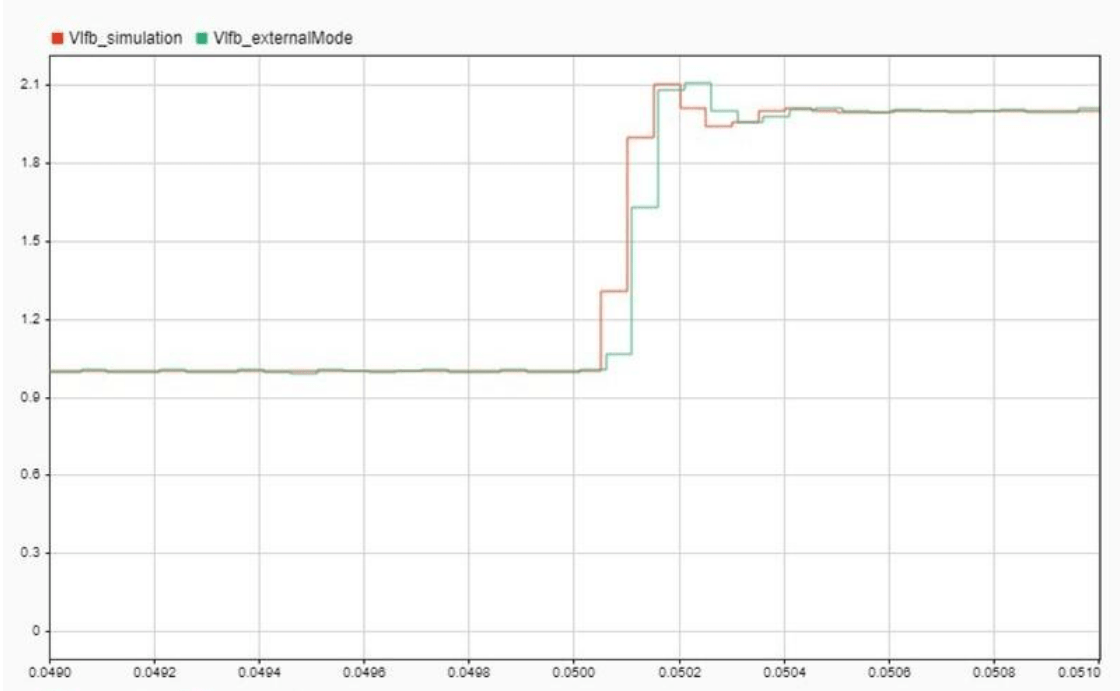

结果

下图显示了从 0 伏到 2 伏的阶跃响应。电压模式控制器能够正确跟踪所需的参考电压。电流低于阈值,算法继续运行,不会中断。还可以观察到,外部模式的结果与仿真模式下获得的输出结果一致。

下图显示,当电流超过 6 安培的阈值时,电流保护算法将被触发。要恢复电源转换功能,必须重置电路板。

当输入电压从 0 伏变为 3 伏时,电流超过 6 安培的阈值,触发电流保护算法。