DVB-S2 HDL Transmitter

This example shows how to implement a digital video broadcasting satellite second generation (DVB-S2) transmitter using Simulink® blocks that are optimized for HDL code generation and hardware implementation.

From this example, you can generate a DVB-S2 transmitter waveform using these steps:

Generate a baseband frame (BBFRAME).

Encode using Bose-Chaudhuri-Hocquenghem (BCH) and low-density parity-check (LDPC) codes.

Interleave, modulate, and generate a physical layer frame (PLFRAME).

Insert dummy frames.

Pulse shape the symbols in frames using a root raised cosine (RRC) filter.

Model Architecture

The BBFRAME Generator block generates BBFRAME from the user packets. The FECFRAME Generator block encodes the BBFRAME using BCH and LDPC coding, and interleaves the encoded frame to generate an FECFRAME. The Symbol Modulator block generates the xFECFRAME by mapping the FECFRAME bits to modulation symbols. The PLFRAME Generator block generates the PLHEADER, pilot symbols, and dummy frames, and multiplexes them with the xFECFRAME bits. The PL Data Scrambler block scrambles the multiplexer output to generate a PLFRAME. The RRC Filtering block pulse shapes the PLFRAME symbols to generate the transmitter waveform.

This figure shows the transmitter frame structure.

File Structure

This example uses supporting files.

dvbs2hdlTransmitter— Model for DVB-S2 HDL transmitter.dvbs2hdlTransmitterCore— Model reference for the transmitter design.dvbs2hdlTxParameters— Functions that generates parameters for thedvbs2hdlTransmitterCoremodel.dvbs2hdlTxInit— Script that initializes thedvbs2hdlTransmittermodel.dvbs2hdlTransmitterVerify— Script that generates reference transmitter waveform usingdvbs2WaveformGenerator(Satellite Communications Toolbox) function and compares the reference waveform with the simulated transmitter output.

System Interface

The figure shows the top-level overview of the dvbs2hdlTransmitter model.

Model Inputs

pktBitsIn — Input packet bits, specified as a Boolean scalar.

pktValidIn — Control signal indicating whether the pktBitsIn is valid, specified as a Boolean scalar.

start — Control signal to capture the TSorGS, UPL, SYNC parameters and to initiate the waveform generation process, specified as a Boolean scalar.

TSorGS — Input stream format, specified as a 2 bit unsigned real integer.

UPL — User packet length (UPL), specified as a 16 bit unsigned real integer.

SYNC — SYNC word, specified as a 8 bit unsigned real integer.

MODCOD — MODCOD, specified as a 5 bit unsigned real integer.

FECFrame — FECFrame type, specified as a Boolean scalar.

Model Outputs:

dataOut — Transmitter output, returned as a 18 bit complex scalar.

validOut — Control signal indicating whether the dataOut is valid, returned as a Boolean scalar.

ready — Control signal indicating whether the transmitter is ready for the input, returned as a Boolean scalar.

nextConfig — Control signal indicating when the new MODCOD and FECFrame configurations are sampled, returned as a Boolean scalar.

Model Structure

This figure shows the structure of the DVB-S2 HDL transmitter subsystem. The subsystem comprises of Stream FIFO, DVB-S2 Tx Core, and RRC Transmit Filter subsystems.

The DVB-S2 Tx Core comprises of BB Frame Generator, FEC Encoder, Interleaver, xFECFrame Generator, PLHeader Generator, and PL Frame Builder, and Ready Generator subsystems.

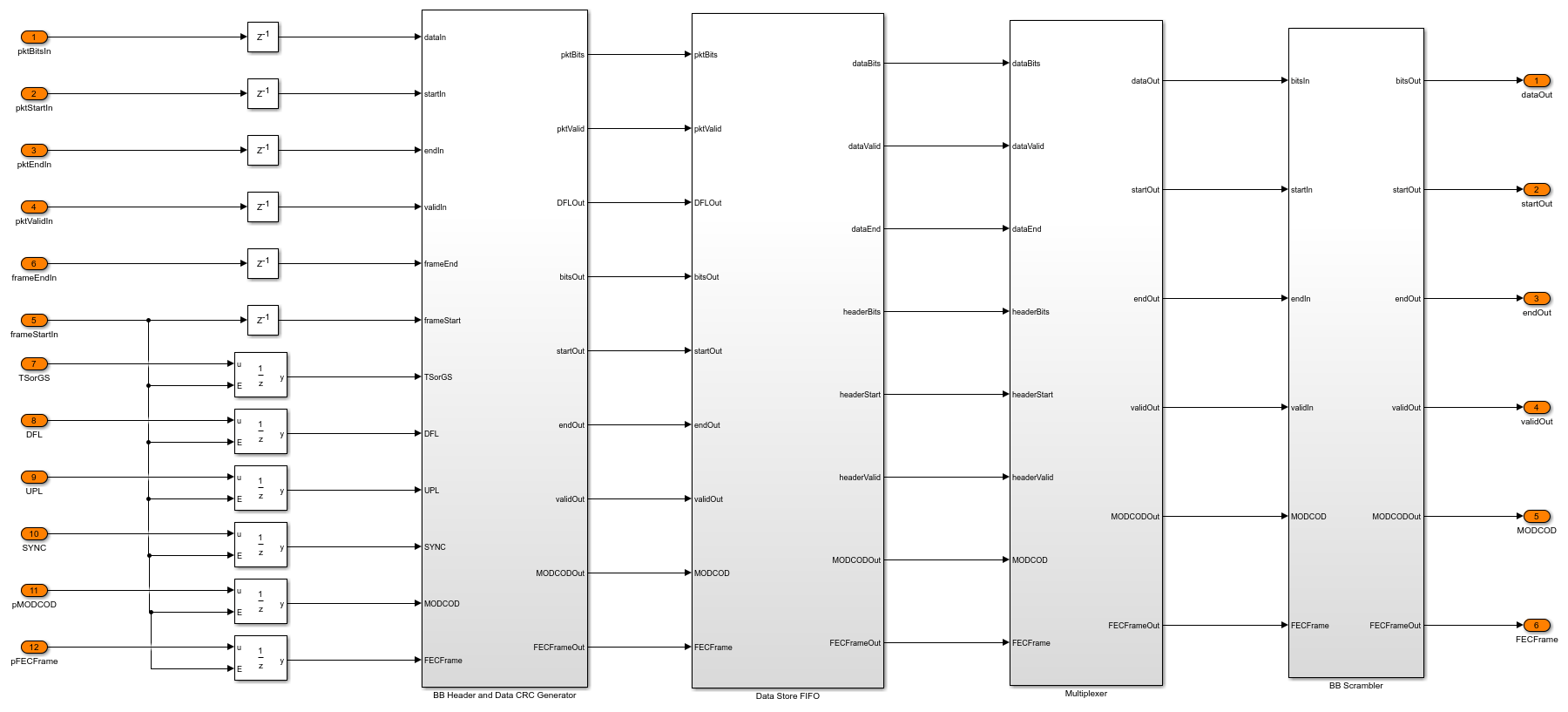

BB Frame Generator

The BB Frame Generator subsystem comprises BB Header and Data CRC Generator, Multiplexer and Zero Padding, and BB Scrambler subsystems. The BB Header and Data CRC Generator subsystem generates BB header, discards the SYNC bits, appends CRC bits to each packet using the General CRC Generator HDL Optimized block. The Multiplexer and Zero Padding subsystem multiplexes the BB header and data field, and appends padding bits to the data field for each frame. The BB Scrambler subsystem scrambles the BB header and data field to generate a BBFRAME.

FEC Encoder

The FEC Encoder subsystem encodes the input bits with BCH Encoder subsystem followed by LDPC Encoder subsystem. For more information, see DVB-S2 HDL BCH Encoder and DVB-S2 HDL LDPC Encoder examples.

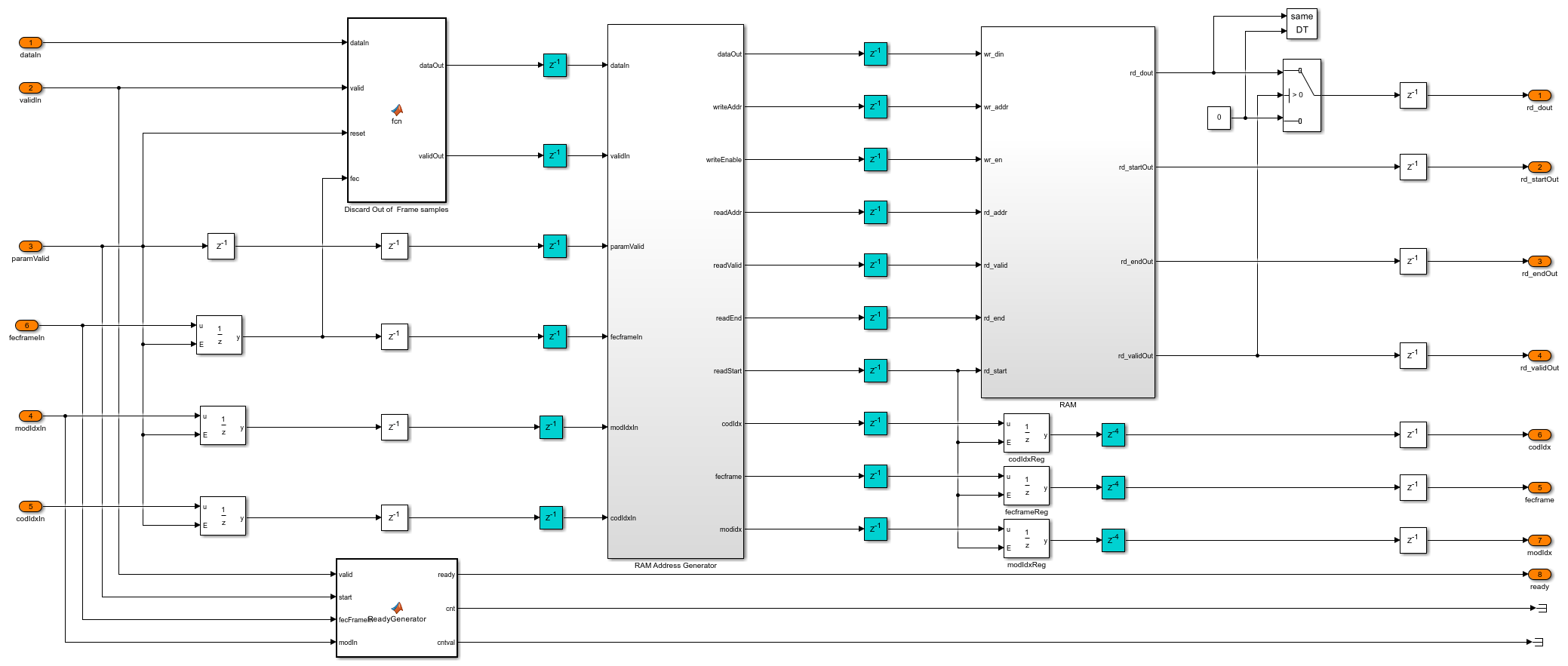

DVB-S2 HDL Interleaver

The DVB-S2 HDL Interleaver subsystem stores encoded bits from the LDPC Encoder subsystem inside the RAM subsystem. The RAM Address Generator subsystem generates read and write addresses for the RAM for interleaving.

In the RAM Address Generator subsystem, the nRows and nColumns subsystem stores the number of rows and columns of each possible configuration in lookup tables (LUT). Based on the MODCOD and FECFrame parameters, the subsystem determines the number of rows and columns for interleaving. The Read Offset Address subsystem generates the interleaver indices of each frame as an offset address. The subsystem reads only two bits for QPSK, three bits for 8-PSK, four bits for 16-APSK, and five bits for 32-APSK in every eight time steps. This process ensures that each symbol covers eight time steps of the interleaver, which is equal to one symbol duration. This subsystem also create empty slots to fit pilots, which are inserted appropriately in the PL Frame Builder subsystem. The Generate and Add Read Base Address subsystem adds the offset address with a base read address to get the address of the bits that are stored in the RAM. The Parameter Store FIFO subsystem stores the parameters and reads them at the start of each frame.

This table shows the rows and columns for deinterleaving in each of the configurations.

Modulation Rows (Normal) Rows (Short) Columns

__________ _____________ ____________ _______

QPSK 64800 16200 1

8-PSK 21600 5400 3

16-APSK 16200 4050 4

32-APSK 12960 3240 5

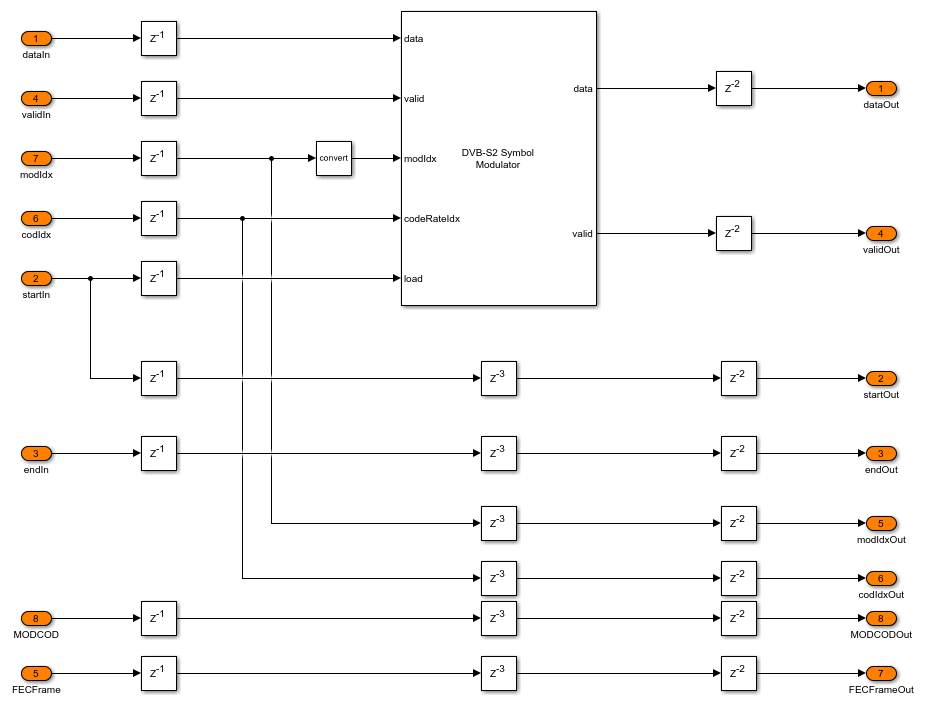

xFECFrame Generator

The xFECFrame Generator subsystem comprises DVB-S2 Symbol Modulator block that maps the input bits to the corresponding modulation symbols.

PLHeader Generator

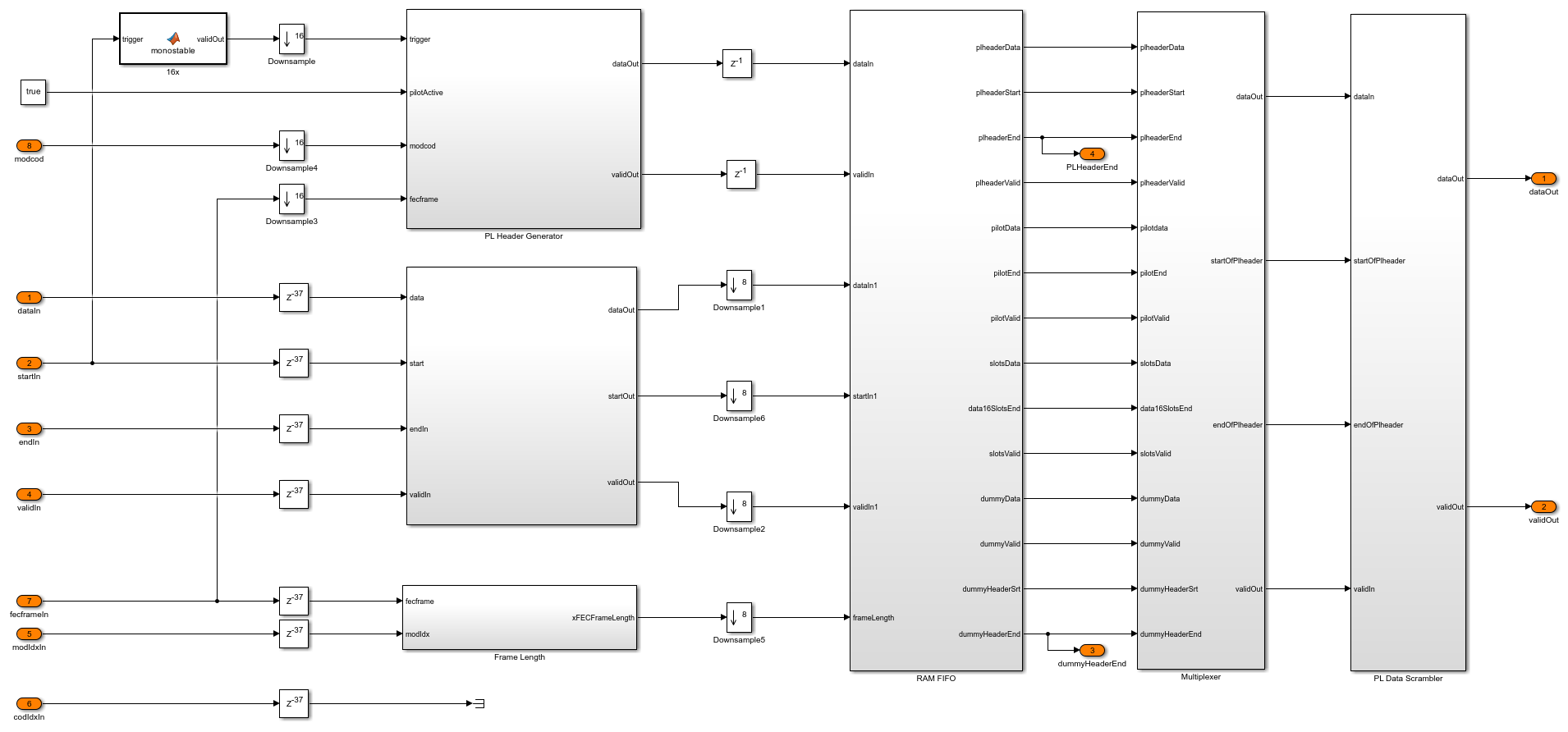

The PL Header Generator subsystem generates the PLHeader symbols for each frame.

PL Frame Builder

The PL Frame Builder multiplexes the PLHeader symbols, pilot symbols, and data symbols according to the frame structure specified in [ 1]. When the time slots come empty Dummy Frame Insertion subsystem fills dummy frames in it. The PL Data Scrambler subsystem scrambles the data field after the PLHeader for each frame and continues until the end of the frame.

RRC Transmit Filter

The RRC Transmit Filter subsystem upsamples the input by a factor of four and uses the Discrete FIR Filter block with an RRC impulse response to pulse shape the PLFRAME symbols.

Run Model

Set the symbol rate, MODCOD, FECFrame type, input stream format, and user packet length on the mask of the Input Configuration subsystem and run the dvbs2hdlTransmitter model. Set the same symbol rate for the Input Configuration subsystem in the dvbs2hdlTransmitter model, the DVB-S2 Tx subsystem of the dvbs2hdlTransmitterCore model reference. Alternatively, execute this command at the MATLAB Command Window to run the model.

sim dvbs2hdlTransmitter

The MODCOD and FECFrame must be row vectors. Each element of the row vectors corresponds to the values of MODCOD and FECFrame in a frame.

Verification and Results

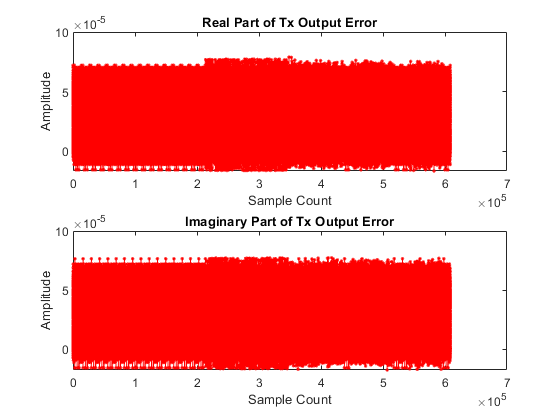

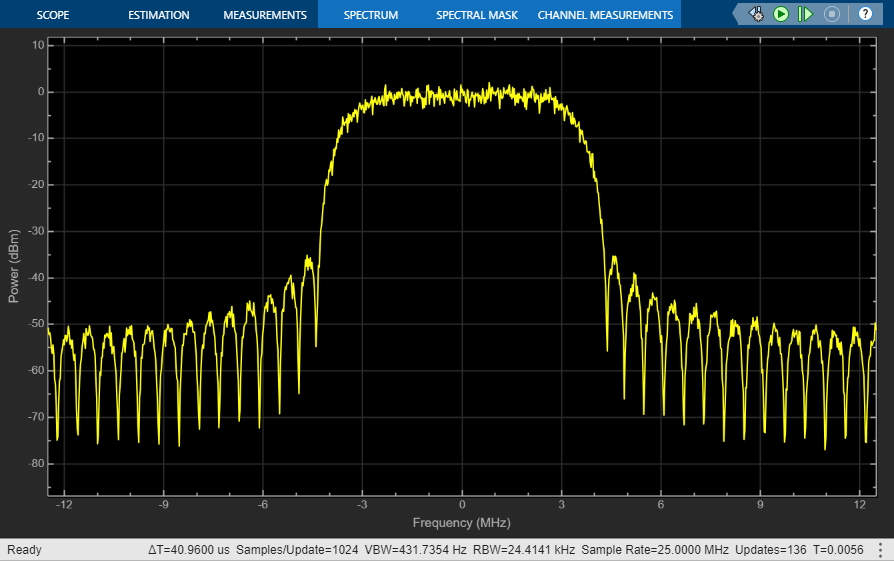

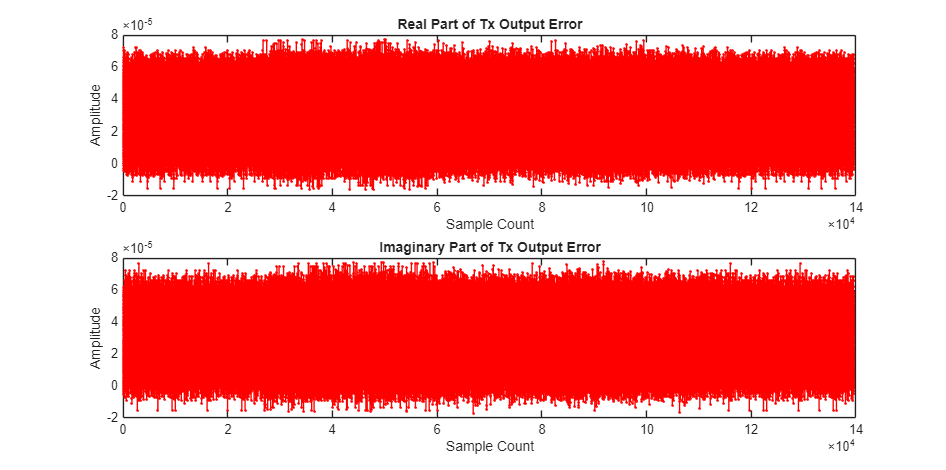

Run the model to display the transmitter spectrum, error plot between the reference waveform and simulation output, and relative mean squared error of the simulation output.

### Searching for referenced models in model 'dvbs2hdlTransmitter'. ### Total of 1 models to build. ### Model reference simulation target for dvbs2hdlTransmitterCore is up to date. Build Summary 0 of 1 models built (1 models already up to date) Build duration: 0h 0m 1.3448s Simulation Completed. Running verification script... Relative mean squared error (dB) between the simulink output and reference = Real: -79.605 Imag: -79.6081

HDL Code Generation

To generate the HDL code for this example, you must have HDL Coder™. Use makehdl and makehdltb functions to generate HDL code and HDL test bench for the DVB-S2 HDL transmitter subsystem. The test bench generation time depends on the simulation time.

The resulting HDL code is synthesized for a Xilinx® Zynq® UltraScale+ RFSoC ZCU111 board. This table shows the post place and route resource utilization. The maximum frequency of operation is 365 MHz.

Resources Usage

_____________ _____

CLB LUT 9124

CLB Registers 9846

RAMB36 30

RAMB18 13

DSP48 44

References

ETSI EN 302 307-1. Digital Video Broadcasting (DVB); Second Generation Framing Structure, Channel Coding and Modulation Systems for Broadcasting, Interactive Services, News Gathering and other Broadband Satellite Applications (DVB-S2).

ETSI TR 102 376-1. Digital Video Broadcasting (DVB); Implementation Guidelines for the Second Generation System for Broadcasting, Interactive Services, News Gathering and other Broadband Satellite Applications (DVB-S2).

See Also

Blocks

Functions

dvbs2WaveformGenerator(Satellite Communications Toolbox)