5G NR HDL Cell Search and MIB Recovery Reference Application

The 5G NR HDL Cell Search and MIB Recovery reference application is an FPGA-proven subsystem IP that performs OFDM demodulation and detects primary and secondary synchronization signals (PSS/SSS), then decodes the master information block (MIB). The FPGA subsystem is designed using Simulink®, and can be used as is or modified to detect and decode the signal synchronization block (SSB) information for use in your 5G wireless application. This video outlines the design methodology used to create it and shows how to simulate it and generate synthesizable RTL for FPGA or ASIC implementation. Details include:

- Creating a reference algorithm and synthesizing a 5G waveform using 5G Toolbox™

- Adding hardware architecture to the MATLAB® reference model

- Implementing streaming versions of the algorithms to handle real-world continuous signal processing

- Simulating and analyzing the Simulink implementation using a MATLAB testbench, and comparing the results versus the MATLAB reference

- Running HDL Coder™ to generate synthesizable RTL, automatically calling FPGA synthesis and returning its results

Published: 4 Dec 2020

The NR HDL Cell Search and MIB Recovery reference applications in Wireless HDL Toolbox are hardware-optimized implementations that you can use to detect and decode 5G new radio signal information as part of your wireless application.

The subsystems from which you will generate HDL are modeled in Simulink because Simulink has a built-in sense of time and helps visualize parallel architectures and fixed-point data type propagation.

Since these started as MATLAB algorithms using 5G Toolbox, we re-used that code to verify our implementations, and that workflow is demonstrated here.

The first step is to partition the functionality that will be deployed to the application, from the testbench. We do that right in MATLAB, while we add some functionality that will be required for deployment, so we can verify the numerics. For instance because this needs to work for real-world over-the-air signals, it includes a digital down converter for mixing to baseband and changing sample rate.

The input waveform is generated from this MATLAB function, also included in this reference application.

On the output side, the MATLAB code will initially display and plot the results, and then print some comparisons versus the reference.

In this diagram, the blue boxes represent test bench elements and the orange represents design. It’s important to do this partitioning early to make it easier to swap in and compare versions with more implementation detail.

There are two major subsystems that are targeted for hardware. The first will perform cell search and detect the primary and secondary synchronization signals, and sometimes that’s all an application needs to use. The second subsystem uses that information to decode the master information block, or MIB.

Focusing on the synchronization signal block detection, it runs in two phases, controlled by a software layer.

The first phase – search mode - takes in the waveform along with a coarse estimate for frequency offset and the desired subcarrier spacing, and performs PSS detection, returning the correlation results for the three possible PSS values. Search mode allows the software to coordinate a search for PSS (or cells) at different coarse frequency offsets and subcarrier spacings. The software determines the strongest PSS correlation, corresponding to the strongest cell, then calls the same hardware subsystem again in demodulation mode, this time passing this PSS info for the hardware to perform OFDM demodulation and SSS detection, returning those results.

There’s also a MATLAB structure of diagnostic signals that gets routed to the top level. This structures the design nicely to later bring these signals up to the top-level of the FPGA for debug.

Finally, the SSB decode subsystem decodes the MIB info from the demodulated resource grid.

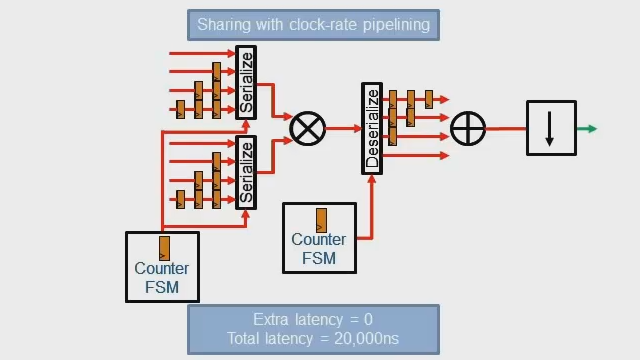

We still need to adapt these algorithms to work on a continuous stream of signal data, as they would in hardware. Simulink is the best environment for that because it models timing.

The MATLAB testbench drives the Simulink model’s inputs, and they get converted to a stream of samples, then back to frames on the output for comparison versus that MATLAB hardware reference algorithm, which in this stage is the reference the testbench will use to verify.

Here we created separate Simulink models for each of the hardware-targeted subsystems. This shows the benefits of partitioning – we can use the MATLAB simulation version of one while we focus on the Simulink details of the other. First the cell search subsystem.

The MATLAB data is passed via the From Workspace blocks here, and the outputs collected for MATLAB in these To Workspace blocks. While we drive the test bench using MATLAB, being able to visualize the architecture and data type propagation makes Simulink more conducive to adding the streaming hardware behavior to the design. Just as with the MATLAB reference, the incoming waveform moves through the DDC to PSS detection in the first mode, the results are returned to the MATLAB testbench acting as the software, and then driven back into the hardware in demodulation mode, where it’s sent into the OFDM demodulator, which is a hardware-ready block you can just plug in and configure. The demodulated grid is output, and also sent into SSS detection, with the results all registered at the system output and returned to MATLAB. You can also see the collecting of diagnostic info for output to the top level.

We can kick off the simulation from MATLAB, and as it starts it generates a plot for the generated test waveform, that shows the combined resource grid of all eight SSBs in the transmitted waveform. The simulation takes a few minutes since it runs both the MATLAB and Simulink, in each mode…so skipping ahead to the results. First the cell search mode results showing PSS0 as the strongest cell, then a nice clean peak from the SSS correlator, and finally the spectrogram showing the demodulated symbols that follow PSS, with SSS in the center 127 resource elements of the second symbol. All of these results and the diagnostics are returned to the MATLAB workspace for analysis.

And then if you want to decode MIB, the MIB recovery reference application adds a block decode module. This module is triggered when the detection block signals it has detected the cell ID. It passes in the cell ID and streams in the grid data. Again this is well-partitioned where it processes the physical broadcast channel, then the broadcast channel using the Polar Decoder IP block, and collects the output using this state machine.

Now, you can use HDL Coder to generate HDL for each of these subsystems. Typically you would use one or both in your application and generate HDL from the whole application. But if you want to try just this reference application deployed to a software-defined radio kit, we also have a version of this design combined together and set up to target a Xilinx Zynq-based SDR. Everything in the HDL workflow advisor is pre-populated, including the mapping of the AXI interfaces to communicate between the hardware and software, and it will generate the HDL, AXI mappings, embedded software, and drivers, and program the board so you can run using live over-the-air signals.

But typically you would use this as-is or make your own modifications to return SSB and MIB info to your 5G-based application.

The reference application overview provides more detail, and the design itself is available in Wireless HDL Toolbox