comm.HDLCRCGenerator

Generate CRC code bits and append to input data

Description

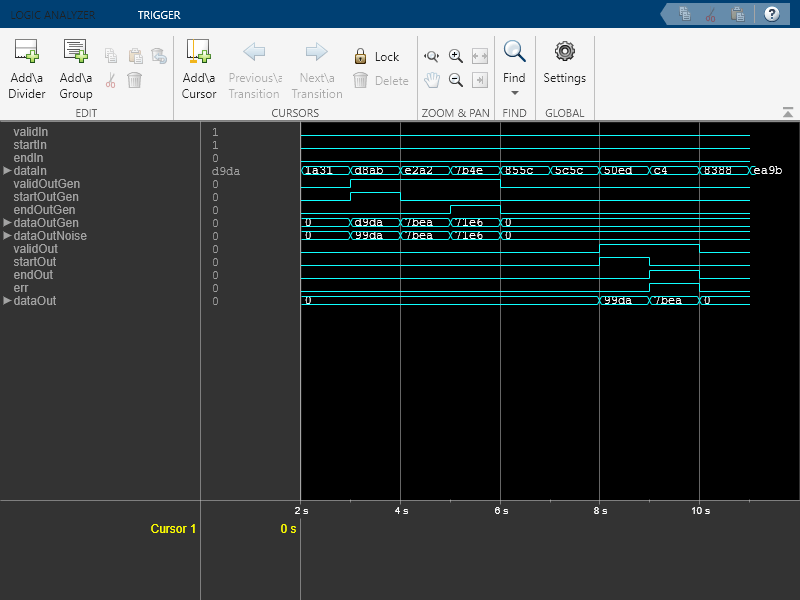

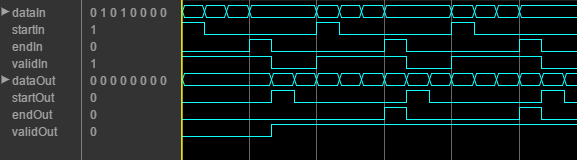

This HDL-optimized cyclic redundancy code (CRC) generator System object™ generates cyclic redundancy code (CRC) bits. Instead of frame processing, the

HDLCRCGenerator

System object processes streaming data. The object has frame synchronization control signals

for both input and output data streams.

To generate cyclic redundancy code bits:

Create the

comm.HDLCRCGeneratorobject and set its properties.Call the object with arguments, as if it were a function.

To learn more about how System objects work, see What Are System Objects?

Creation

Syntax

Description

CRCGen = comm.HDLCRCGeneratorCRCGen. This object generates CRC bits according to a

specified generator polynomial and appends them to the input data.

CRCGen = comm.HDLCRCGenerator(Name,Value)

CRCGen = comm.HDLCRCGenerator('Polynomial',[1 0 0 0 1 0 0 0 0], ...

'FinalXORValue',[1 1 0 0 0 0 0 0]);CRCGen = comm.HDLCRCGenerator(poly,Name,Value)Polynomial property to

poly, and the other specified property names to the specified

values.

Properties

Usage

Description

Input Arguments

Output Arguments

Object Functions

To use an object function, specify the

System object as the first input argument. For

example, to release system resources of a System object named obj, use

this syntax:

release(obj)

Examples

Algorithms

Extended Capabilities

Version History

Introduced in R2012a