HDL 代码生成

要在 FPGA 或 ASIC 上实现 DSP 设计,请使用 HDL Coder™ 从 Simulink 或 MATLAB 生成代码。该工具用于生成可综合和可移植的 VHDL® 和 Verilog® 代码,还生成 VHDL 和 Verilog 测试平台,用于对生成的代码进行快速仿真、测试和验证。

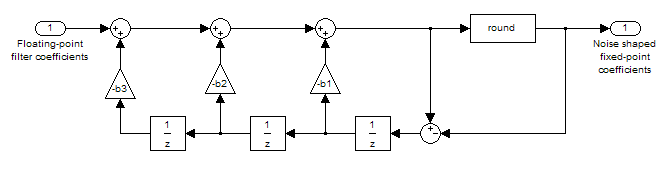

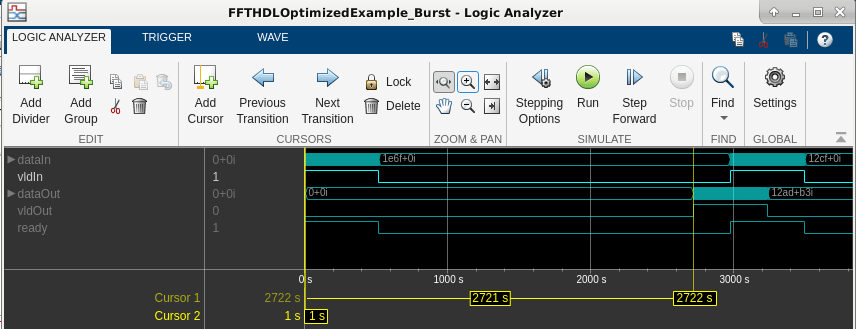

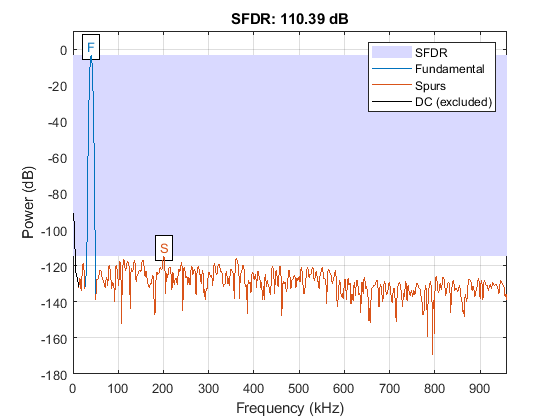

DSP System Toolbox™ 和 DSP HDL Toolbox 中支持的模块包括滤波器、数学和信号运算,以及其他针对资源使用和性能而优化的算法,如 FFT (DSP HDL Toolbox)、Discrete FIR Filter (DSP HDL Toolbox) 和 NCO (DSP HDL Toolbox) 模块。DSP HDL Toolbox™ 提供实现硬件友好架构的模块和 System object。DSP HDL Toolbox 模块和 System object 还具有高吞吐量的流接口,以实现每秒千兆次采样 (GSPS)(亦称超采样率),并提供硬件控制信号以及用于选择不同算法硬件实现的选项。

有关如何使用 HDL Coder 从 DSP System Toolbox 模块生成 HDL 代码的示例,请参阅Multichannel FIR Filter for FPGA。有关 DSP HDL Toolbox 的介绍,请参阅 Implement FFT Algorithm for FPGA (DSP HDL Toolbox)。要从 System object™ 生成 HDL 代码,请参阅Generate HDL Code for IIR Filter (DSP HDL Toolbox)。

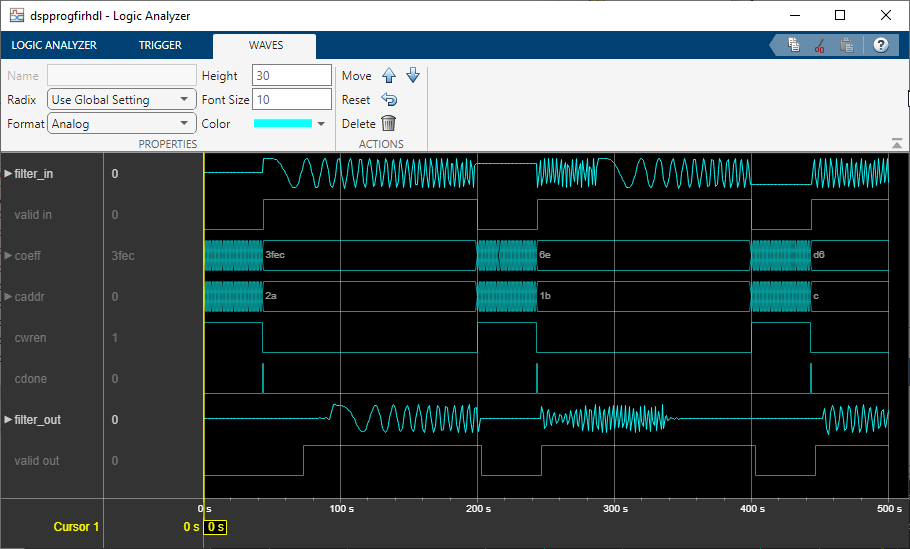

要在 Simulink 或 MATLAB 中调试您的设计,请使用逻辑分析仪波形查看器。

Simulink 可视化工具

| 逻辑分析仪 | 可视化、测量并分析一段时间内的转移和状态 |

主题

- Find Blocks That Support HDL Code Generation

Filter for blocks that support HDL code generation in the Simulink library browser and in documentation.

- High-Throughput HDL Algorithms (DSP HDL Toolbox)

Choose a block that supports frame-based processing for HDL code generation.

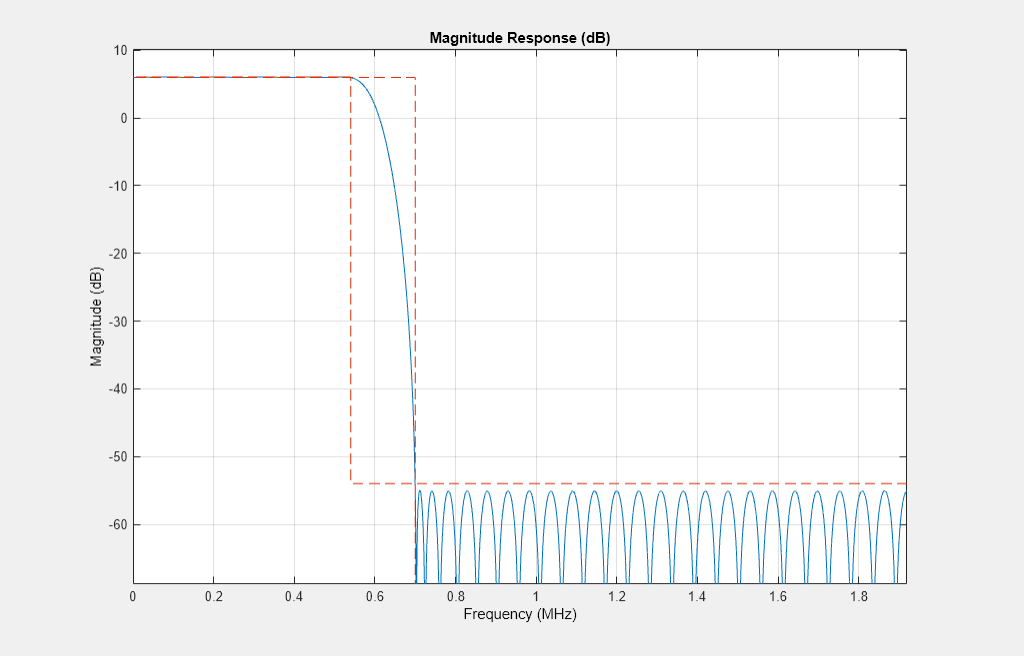

- HDL Filter Architectures

HDL code generation parameters to control speed and area tradeoffs in filter architectures.

- Subsystem Optimizations for Filters

Select resource sharing and pipeline optimization options.

- Visualize Multiple Signals Using Logic Analyzer

Visualize multiple signals of a programmable FIR filter by using the Logic Analyzer app.

- Generate HDL Code for IIR Filter (DSP HDL Toolbox)

Design and generate HDL code for a DC blocking filter in MATLAB.