Generate SIMD Code from Simulink Blocks for Apple silicon Platforms

You can generate single instruction, multiple data (SIMD) code from certain Simulink® blocks by using ARM® Neon technology for Apple silicon platforms. SIMD is a computing paradigm in which a single instruction processes multiple data. Many modern processors have SIMD instructions that, for example, perform several additions or multiplications at once. For computationally intensive operations on supported blocks, SIMD intrinsics can significantly improve the performance of the generated code on Apple silicon platforms.

To generate SIMD code for Intel® platforms, see Generate SIMD Code from Simulink Blocks for Intel Platforms.

Blocks That Support SIMD Code Generation for Apple

When certain conditions are met, you can generate SIMD code by using ARM Neon technology for Apple silicon platforms. This table lists blocks that support SIMD code generation. The table also details the conditions under which the support is available. Some other blocks support SIMD code generation when they generate control flow code that the code generator can convert to vectorized code. For example, the code generator can replace some for-loops that contain conditional expressions with SIMD instructions.

| Block | Conditions |

|---|---|

| Sum (Add) | The input signal is of data type single, int8,

int16, int32,

int64, uint8,

uint16,

uint32, or

uint64. |

| Sum (Subtract) | The input signal is of data type single, int8,

int16, int32,

int64, uint8,

uint16,

uint32, or

uint64. |

| Sum (Sum of Elements) |

|

| Product, Matrix Multiply (Product) | The input signal is of data type single, int8, int16, int32, uint8, uint16, or uint32. |

| Product, Matrix Multiply (Product of Elements) |

|

| Gain |

|

| Abs | The input signal is of data type single. |

| MinMax | The input signal is of data type single. |

| MinMax (MinMax of Elements) |

|

| MATLAB Function | MATLAB code meets the conditions specified in Generate SIMD Code from MATLAB Functions for ARM Platforms. |

| For Each Subsystem |

|

| Bitwise Operator |

|

| Shift Arithmetic | The input signal is of data type int8, int16, or

int32. |

| Relational Operator | The input signal is of data type single,

int32, or

uint32. |

| Data Type Conversion |

|

If you have DSP System Toolbox™, you can also generate SIMD code from certain DSP System Toolbox blocks. For more information, see Simulink Blocks in DSP System Toolbox that Support SIMD Code Generation (DSP System Toolbox).

Generate Plain C Code and SIMD Code for Apple

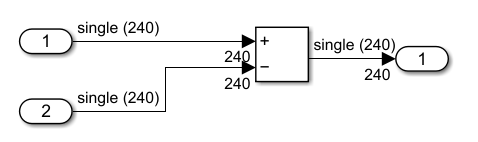

For this example, create a simple model simdDemo that has a

Subtract block. The Subtract block has an input signal that

has a dimension of 240 and an input data type of single.

The generated plain C code for this model is:

void simdDemo_step(void)

{

int32_T i;

for (i = 0; i < 240; i++) {

simdDemo_Y.Out1[i] = simdDemo_U.In1[i] - simdDemo_U.In2[i];

}

}To generate SIMD code:

Open the Embedded Coder® app.

In the C Code tab, click Settings > Hardware Implementation.

Select a hardware target that supports SIMD code generation. Set these parameters:

Hardware board —

NoneDevice vendor —

AppleDevice type —

ARM 64

On the Optimization pane, from the Leverage target hardware instruction set extensions list, select

Neon v7. TheNeon v7instruction set supports target hardware ARM v7 and above, including ARM v8 and ARM v9.Optionally, select the Optimize reductions parameter to generate SIMD code for reduction operations or the FMA parameter to generate SIMD code for fused multiply-add operations.

Generate code from the model.

for (i = 0; i <= 236; i += 4) {

vst1q_f32(&simdDemo_Y.Out1[i], vsubq_f32(vld1q_f32(&simdDemo_U.In1[i]),

vld1q_f32(&simdDemo_U.In2[i])));

}The SIMD instructions are the intrinsic functions that start with the identifier

v. The functions process multiple data in a single iteration of the

loop because the loop increments by four for single data types. For models that process more

data and are computationally more intensive than this one, the presence of SIMD instructions

can significantly speed up the code execution time.