为 Simulink 模型生成 SystemVerilog 代码

此示例说明如何从 Simulink® 模型生成 SystemVerilog HDL 代码。与 Verilog® 代码相比,SystemVerilog 代码具有更高级的功能,例如使用数组端口、包声明、结构体端口等。

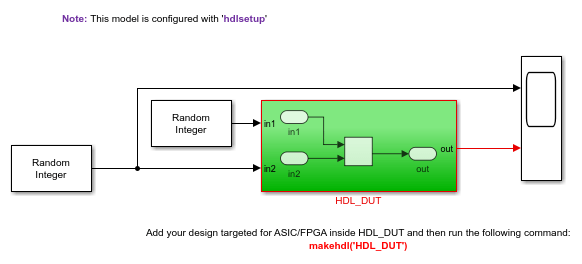

打开模型

打开 SystemVerilogFromSimulink 模型。该模型将类型为 uint8 的两个向量输入相加并输出结果。

mdl = 'SystemVerilogFromSimulink'; dut = [mdl '/HDL_DUT']; open_system(mdl);

在 Simulink 中生成 SystemVerilog 代码

要生成 SystemVerilog 代码,请执行以下操作:

在 Simulink® 工具条的建模选项卡中,点击模型设置以打开“配置参数”对话框。

在 HDL 代码生成窗格中,将语言设置为

SystemVerilog。点击确定。在 Simulink® 的 App 选项卡中点击 HDL Coder。

选择要为其生成 SystemVerilog 代码的子系统。对于

SystemVerilogFromSimulink模型,在 HDL Code 选项卡中,将以下项的代码参数设置为HDL_DUT。通过点击生成 HDL 代码为

HDL_DUT子系统生成 SystemVerilog 代码。

从 MATLAB 命令行窗口生成 SystemVerilog 代码

您也可以使用 makehdl 函数为您的在测设计 (DUT) 生成 SystemVerilog 代码。在 MATLAB® 命令行窗口中运行以下命令,为 HDL_DUT 子系统生成代码。

load_system(mdl); hdlset_param(mdl, 'TargetLanguage', 'SystemVerilog'); makehdl(dut)

### Working on the model <a href="matlab:open_system('SystemVerilogFromSimulink')">SystemVerilogFromSimulink</a>

### Generating HDL for <a href="matlab:open_system('SystemVerilogFromSimulink/HDL_DUT')">SystemVerilogFromSimulink/HDL_DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('SystemVerilogFromSimulink', { 'HDL Code Generation' } )">SystemVerilogFromSimulink</a> for HDL code generation parameters.

### Running HDL checks on the model 'SystemVerilogFromSimulink'.

### Begin compilation of the model 'SystemVerilogFromSimulink'...

### Working on the model 'SystemVerilogFromSimulink'...

### Working on... <a href="matlab:configset.internal.open('SystemVerilogFromSimulink', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_SystemVerilogFromSimulink'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/SystemVerilogFromSimulink/gm_SystemVerilogFromSimulink.slx')">hdlsrc/SystemVerilogFromSimulink/gm_SystemVerilogFromSimulink.slx</a>

### Begin SystemVerilog Code Generation for 'SystemVerilogFromSimulink'.

### Working on SystemVerilogFromSimulink/HDL_DUT as hdlsrc/SystemVerilogFromSimulink/HDL_DUT.sv.

### Generating package file hdlsrc/SystemVerilogFromSimulink/HDL_DUT_pkg.sv.

### Code Generation for 'SystemVerilogFromSimulink' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3710757/tp4873507c/hdlcoder-ex97853341/hdlsrc/SystemVerilogFromSimulink', '/tmp/Bdoc26a_3146167_3710757/tp4873507c/hdlcoder-ex97853341/hdlsrc/SystemVerilogFromSimulink/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3710757/tp4873507c/hdlcoder-ex97853341/hdlsrc/SystemVerilogFromSimulink/HDL_DUT_report.html

### HDL check for 'SystemVerilogFromSimulink' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

在 HDL 代码生成完成后,打开生成的 SystemVerilog 文件以检查为您的 DUT 生成的代码。生成的 SystemVerilog 代码具有用于 DUT 接口的向量端口声明。HDL Coder 还会为 DUT 端口的 typedef 声明生成包文件。