Bits to Word

Libraries:

HDL Coder /

Logic and Bit Operations

Description

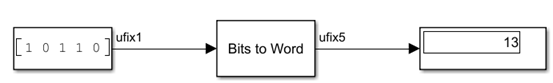

The Bits to Word block converts a length-N input vector of bits to an N-bit integer. The output of the block is an unsigned integer that has word length N.

The block treats the first element of the input vector as the least significant bit (LSB)

of the output and treats subsequent bits as the next significant bits in ascending order. This

figure shows the conversion of the bit vector [1 0 1 1 0] to the integer

value 13.