基本 HDL 算法

使用基本 Simulink® 模块创建简单 HDL 设计

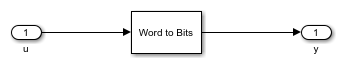

HDL Coder 模块库包含许多基本模块,您可将其添加到 Simulink 建模环境并开发 HDL 算法。这些模块包括输入源、输出信宿及执行基础到复杂数学和三角运算的模块。

要过滤 Simulink 库浏览器以仅显示 HDL 支持的模块,请输入 hdllib。本节列出的模块包括仅在 HDL Coder 库中可用的模块。Add 和 Product 等模块在库浏览器的 Simulink 库中提供。

有关过滤后的支持 HDL 代码生成的 Simulink 模块的列表,请参阅 Simulink 模块列表(HDL 代码生成)。

函数

hdllib | 显示与 HDL 代码生成兼容的模块 |

检查

模块

主题

基础建模

- Model and Debug Test Point Signals with HDL Coder

An example that shows how to add test points to signals in your model and debug these signals in the generated HDL code. - Generate DUT Ports for Tunable Parameters

Generate tunable parameters as top-level DUT ports. - Generate HDL Code with Annotations or Comments

How to add annotations to generated HDL code using the DocBlock and model annotations. - Scalarization of Vector Ports in Generated VHDL Code

Flatten vector signals on entire model or at DUT level into a structure of scalar signals in generated VHDL or SystemVerilog code. - 对 Float Typecast 模块进行仿真并为其生成 HDL 代码

使用 Float Typecast 模块将输入强制转换为浮点或定点。

数据类型支持

- Supported Data Types and Scope

MATLAB® data type and scope support for HDL code generation. - Signal and Data Type Support

HDL code generation support for signal types and data types.