Configure Custom Synthesis Attributes for Simulink Blocks

This example shows how to configure custom synthesis attributes for a Simulink model using the command-line interface and propagate them to the generated HDL code. You can assign the custom attributes to the Simulink blocks or the design under test (DUT) based on the synthesis tool, and generate HDL code that includes the corresponding synthesis attributes.

Open Model

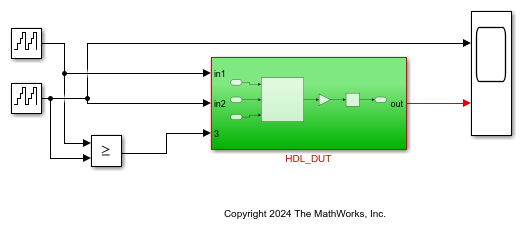

Open the model. This model contains Single Port RAM System, Gain, and Delay blocks.

mdl = 'SynthesisAttributesExampleModel'; dut = [mdl '/HDL_DUT']; open_system(mdl);

Set Custom Synthesis Attributes

You can set synthesis attributes for the blocks and subsystems in the model by using hdlset_param function. In this example, the ram_style synthesis attribute is set on the Single Port RAM block; the use_dsp synthesis attribute is set on the Gain block; the max_fanout and mark_debug synthesis attributes are set on the Delay block; and the keep_hierarchy synthesis attribute is set on the Subsystem. This example uses the Xilinx® Vivado® synthesis tool.

hdlset_param([dut '/SinglePortRAMSystem'], 'SynthesisAttributes', {{'ram_style', 'ultra'}}); hdlset_param([dut '/Gain'], 'SynthesisAttributes', {{'use_dsp', 'yes'}}); hdlset_param([dut '/Delay'], 'SynthesisAttributes', {{{'max_fanout', '5'}},{{'mark_debug', 'true'}}}); hdlset_param(dut, 'SynthesisAttributes', {{'keep_hierarchy', 'yes'}});

Alternatively, you can use the HDL Block Properties dialog box to set synthesis attributes. For more information, see SynthesisAttributes.

Generate HDL Code

You can generate VHDL code for your design under test by using the makehdl function. Because synthesis attributes are independent of target language, you can use the same synthesis attributes to generate Verilog and SystemVerilog code. To generate VHDL code for DUT subsystem, run this command in your MATLAB® command window.

load_system(mdl); makehdl(dut, 'TargetLanguage', 'VHDL');

### Working on the model <a href="matlab:open_system('SynthesisAttributesExampleModel')">SynthesisAttributesExampleModel</a>

### Generating HDL for <a href="matlab:open_system('SynthesisAttributesExampleModel/HDL_DUT')">SynthesisAttributesExampleModel/HDL_DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('SynthesisAttributesExampleModel', { 'HDL Code Generation' } )">SynthesisAttributesExampleModel</a> for HDL code generation parameters.

### Running HDL checks on the model 'SynthesisAttributesExampleModel'.

### Begin compilation of the model 'SynthesisAttributesExampleModel'...

### Working on the model 'SynthesisAttributesExampleModel'...

### Working on... <a href="matlab:configset.internal.open('SynthesisAttributesExampleModel', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_SynthesisAttributesExampleModel'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/SynthesisAttributesExampleModel/gm_SynthesisAttributesExampleModel.slx')">hdlsrc/SynthesisAttributesExampleModel/gm_SynthesisAttributesExampleModel.slx</a>

### Begin VHDL Code Generation for 'SynthesisAttributesExampleModel'.

### Working on SynthesisAttributesExampleModel/HDL_DUT/SinglePortRAM_generic as hdlsrc/SynthesisAttributesExampleModel/SinglePortRAM_generic.vhd.

### Working on SynthesisAttributesExampleModel/HDL_DUT as hdlsrc/SynthesisAttributesExampleModel/HDL_DUT.vhd.

### Generating package file hdlsrc/SynthesisAttributesExampleModel/HDL_DUT_pkg.vhd.

### Code Generation for 'SynthesisAttributesExampleModel' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1590811/tp28802261/hdlcoder-ex62929635/hdlsrc/SynthesisAttributesExampleModel', '/tmp/Bdoc26a_3233028_1590811/tp28802261/hdlcoder-ex62929635/hdlsrc/SynthesisAttributesExampleModel/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1590811/tp28802261/hdlcoder-ex62929635/hdlsrc/SynthesisAttributesExampleModel/HDL_DUT_report.html

### HDL check for 'SynthesisAttributesExampleModel' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

Code Generation Output

HDL Coder™ generates the SinglePortRAM_generic.vhd file. The generated VHDL code includes the synthesis attributes, as shown in the following code snippet.

ATTRIBUTE ram_style : string;

ATTRIBUTE ram_style OF ram : SIGNAL IS "ultra";

HDL Coder also includes synthesis attributes in the HDL_DUT.vhd file.

ATTRIBUTE keep_hierarchy : string; ATTRIBUTE keep_hierarchy OF rtl : ARCHITECTURE IS "yes";

ATTRIBUTE use_dsp : string; ATTRIBUTE max_fanout : integer; ATTRIBUTE mark_debug : boolean;

ATTRIBUTE use_dsp OF Gain_out1 : SIGNAL IS "yes"; ATTRIBUTE max_fanout OF Delay_reg : SIGNAL IS 5; ATTRIBUTE mark_debug OF Delay_out1 : SIGNAL IS true;