Generating HDL Code for Subsystems with Array of Buses

An array of buses is an array whose elements are buses. Each element in an array of buses must be nonvirtual and must have the same data type.

The array of buses represents structured data compactly. The array:

Reduces the model complexity

Reduces maintenance by organizing and routing signals in your Simulink® model for vectorized algorithms

For more information, see Group Nonvirtual Buses in Arrays of Buses.

You can generate HDL code for virtual and nonvirtual blocks that Simulink supports with an array of buses. For more information, see Bus-Capable Blocks.

How HDL Coder Generates Code for Array of Buses

HDL Coder™ expands the array of buses in your Simulink model into the corresponding scalar signals in the generated code.

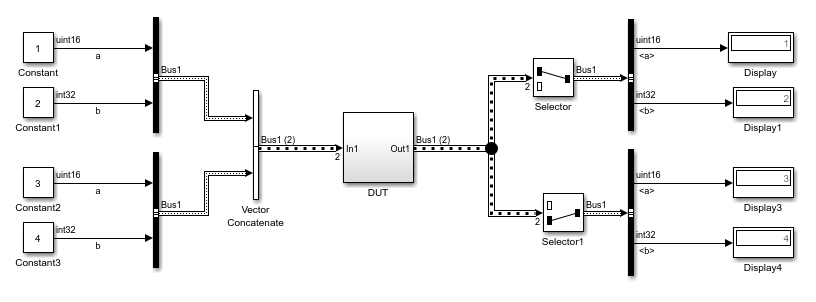

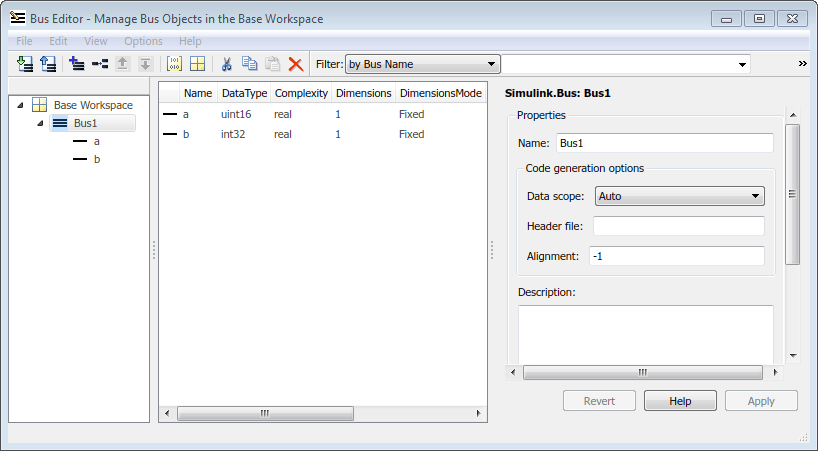

This Simulink model has an array of buses signal at the DUT interface.

The array of buses combines two nonvirtual bus elements, each having scalars

a and b of types uint16 and

int32 respectively.

The resulting HDL code expands the array of buses into scalars, and contains four scalar input and output ports.

In the generated code, the array of bus expansion results in four scalar signals at the

input and output ports. For the first bus object, the input ports are

In_1_a and In_1_b. For the second bus object, they

are In_2_a and In_2_b. At the output, for the first

bus object, they are Out_1_a and Out_1_b. For the

second bus object, they are Out_2_a and

Out_2_b.

ENTITY DUT IS

PORT( In1_1_a : IN std_logic_vector(15 DOWNTO 0); -- uint16

In1_1_b : IN std_logic_vector(31 DOWNTO 0); -- int32

In1_2_a : IN std_logic_vector(15 DOWNTO 0); -- uint16

In1_2_b : IN std_logic_vector(31 DOWNTO 0); -- int32

Out1_1_a : OUT std_logic_vector(15 DOWNTO 0); -- uint16

Out1_1_b : OUT std_logic_vector(31 DOWNTO 0); -- int32

Out1_2_a : OUT std_logic_vector(15 DOWNTO 0); -- uint16

Out1_2_b : OUT std_logic_vector(31 DOWNTO 0) -- int32

);

END DUT;HDL Coder generates code in accordance with the order in which you specify the bus elements and the array elements in your Simulink model. If you specify the VHDL® target language for your Simulink model that contains a bus object with arrays, HDL Coder preserves the arrays in the generated code, and does not expand into scalars.

Array of Buses Limitations

Do not use the array of buses inside other data types. You cannot use a bus signal that contains an array of buses.

MATLAB System and MATLAB Function blocks that contain System objects are not supported with an array of buses.