层次化设计与同步硬件行为

HDL Coder 模块库包含许多模块,您可将其添加到 Simulink® 建模环境并开发 HDL 算法。要进行大型设计建模,您可以将模型划分为若干子系统并创建层次化设计。为实现同步硬件行为并生成硬件友好的 HDL 代码,请在子系统内使用 State Control 模块。

要过滤 Simulink 库浏览器以仅显示 HDL 支持的模块,请输入 hdllib。本节列出的模块包括仅在 HDL Coder 库中可用的模块。Foreach Subsystem 和 Atomic Subsystem 等模块在库浏览器的 Simulink 库中提供。

有关经过过滤的 HDL 代码生成支持的 Simulink 模块的列表,请参阅 Simulink 模块列表(HDL 代码生成)。

函数

hdllib | 显示与 HDL 代码生成兼容的模块 |

检查

模块

主题

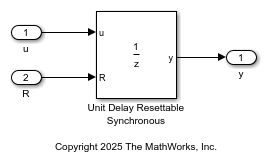

- Synchronous Subsystem Behavior with the State Control Block

Description of a State Control Block and how it generates cleaner HDL code.

- Generating HDL Code for Subsystems with Array of Buses

Generate HDL code for subsystems that use array of buses in the design.

- Generate Reusable Code for Subsystems

Generate shared code for identical subsystems or subsystems identical except for their mask parameter values.

- Generate Parameterized Code for Referenced Models

Generate VHDL®

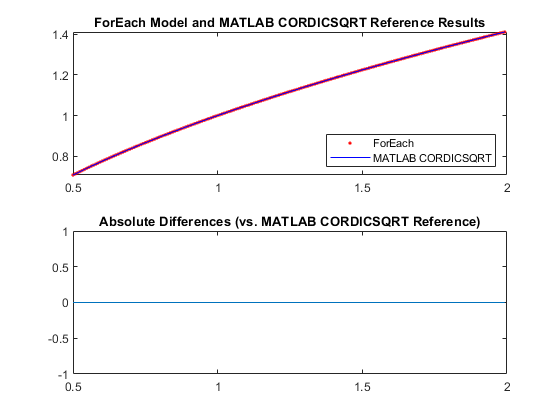

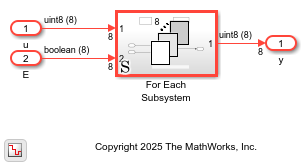

generic, Verilog® or SystemVerilogparameterfor model arguments in a model reference. - Generate HDL Code for Blocks Inside For Each Subsystem

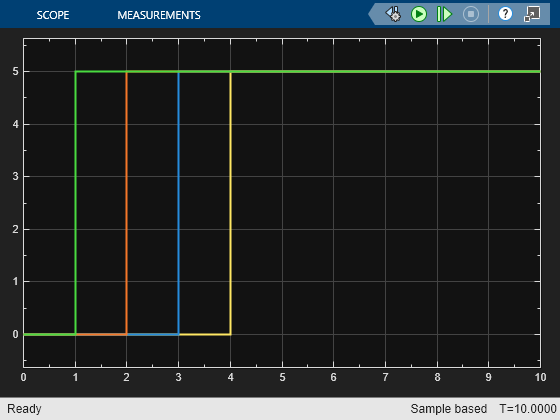

An example that shows how to model and generate HDL code for blocks inside a For Each Subsystem.

- Model Referencing for HDL Code Generation

Generate HDL code for referenced models.

- Generate Incremental HDL Code for Referenced Models

When incremental code is generated for referenced models.

- Set Configuration Parameters for HDL Code Generation of Model Hierarchies

Satisfy model reference hierarchy requirements to enable HDL code generation.

- Generate HDL Code with Record or Structure Types for Bus Signals

Generate VHDL code with record or structure types for bus signals at different subsystem-level interfaces.