Getting Started with RAM and ROM in Simulink

This example shows how to utilize RAM resources in your FPGA design using HDL Coder™.

Introduction

Dedicated RAM blocks on an FPGA are valuable resources for digital designs. It is easy to design with RAM and ROM in Simulink® and utilize the dedicated RAM blocks available on your FPGA using HDL Coder.

RAM Blocks in the HDL Example Library

HDL Coder provides these types of RAM blocks in the HDL RAMs block library. Use hdllib to display blocks that are compatible with HDL Coder™, and then select the HDL RAMs library under HDL Coder:

Single Port RAM

Single Port RAM System

Simple Dual Port RAM

Simple Dual Port RAM System

Dual Port RAM

Dual Port RAM System

Dual Rate Dual Port RAM

Run this command to navigate to the RAM blocks in the HDL library.

hdllib

The RAM blocks are masked subsystems built using Simulink blocks for behavioral simulation. For code generation, HDL Coder generates predefined templates that describe RAM structures in HDL. Most synthesis tools recognize the RAM structures in the templates, and map them to available RAM resources on the FPGA.

Using Generic RAM Coding Style for RAM Blocks

By default, HDL Coder provides RAM templates that use clock enable for the RAM structures. As an alternative, HDL Coder also provides a style of generic template that does not use clock enable. The generic RAM style template implements clock enable with logic in a wrapper around the RAM. You can control this using RAM Architecture option in the HDL Coder global settings panel.

You may want to use the generic RAM style if your synthesis tool does not support RAM structures with a clock enable and cannot map the HDL to FPGA RAM resources as a result.

The example hdlcoderfirram shows how to use the generic RAM style for your design.

open_system('hdlcoderfirram'); open_system('hdlcoderfirram/FIR_RAM');

Selecting a RAM Coding Style

You can select a RAM coding style from the Configuration Parameters window. In the Simulink Toolstrip, in the Apps tab, select HDL Coder. In the HDL Code tab, select Settings. In HDL Code Generation > Global Settings > Coding style, set the RAM Architecture parameter to your desired RAM coding style.

The RAM Architecture parameter controls the generation of clock enable logic for RAM in a subsystem and determines how HDL Coder implements clock enable signals when it generates HDL code for RAM.

By default, RAM Architecture is set to RAM with clock enable. HDL Coder generates HDL code for RAM that uses a dedicated clock enable signal. The availability of a dedicated clock enable signal depends on your FPGA hardware specifications.

If you set RAM Architecture to Generic RAM without clock enable, HDL Coder generates HDL code for RAM that does not support a clock enable signal. Instead, HDL Coder generates a RAM wrapper that implements the clock enable logic. Use this setting if you use a synthesis tool that does not support RAM with a clock enable signal or target hardware that does not properly map the generated HDL code for RAM to the FPGA RAM resources.

Building ROM Using Simulink Blocks

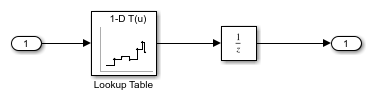

HDL Coder does not provide a ROM block, but you can build one using a Lookup Table block and a Unit Delay block from Simulink, as shown in the following example.

open_system('hdlcoderrom'); open_system('hdlcoderrom/ROM');

Follow these modeling guidelines when building ROM from Simulink:

For an n-bit address, specify all

entries of the Lookup Table data. Otherwise, your synthesis tool may not map the generated code to RAM, and the code may not match your Simulink model.

entries of the Lookup Table data. Otherwise, your synthesis tool may not map the generated code to RAM, and the code may not match your Simulink model.Place the Lookup Table and Unit Delay blocks in the same model hierarchy.

Support of RAM reset logic varies among FPGA devices and synthesis tools. For best synthesis results, suppress the generation of reset logic for the Unit Delay block by setting its ResetType property to

none, in the HDL Block Properties dialog box. Also set the IgnoreDataChecking property to 1 in the HDL Test Bench configuration parameters to ignore the initial simulation mismatch caused by suppressing the reset logic.

If you follow these guidelines, most synthesis tools will implement the ROM using dedicated RAM blocks in an FPGA.

Minimum RAM Size Requirements

If the size of the RAM or ROM in your design is small, your synthesis tool may map the generated code to registers instead of dedicated RAM resources for better speed performance. Check your synthesis tool for minimum RAM size requirements, and if desired, how you may override those requirements.