Use Triggered Subsystem in HDL Code Generation

The Triggered Subsystem block models subsystems that execute each time the control signal reaches a trigger value. By using triggered subsystem in HDL code generation, you can:

Model a task that executes upon the detection of a trigger value.

Use the trigger signal as a clock setting to model trigger port of the triggered subsystem as a clock signal.

Generate clock and reset signals in the HDL code by combining a triggered subsystem with a resettable subsystem.

Generating HDL Code from Triggered Subsystem

When generating code from models that include triggered subsystems, consider these guidelines:

To prevent the code generator from inserting extra bypass registers in the HDL code, put unit delays on the output signals of Triggered Subsystem blocks.

To match the synthesis results with the Simulink® results, drive the trigger port with registered logic and synchronous clock on the FPGA.

Using triggered subsystems can affect synthesis results. The system clock speed might decrease slightly and generated code may require more resources. The resource usage increases with the number of triggered subsystems and number of output ports per subsystem.

When using Unit Delay Enabled Synchronous block inside the triggered subsystem, place a State Control block with synchronous semantics in the Triggered Subsystem.

When you connect outputs from a Signal Editor block to a triggered subsystem, use a Rate Transition block to run all triggered subsystem ports at the same rate. For example,

If the trigger input source is a Signal Editor block and the other triggered subsystem inputs come from other sources, insert a Rate Transition block into the signal path before the trigger input.

If all inputs, including the trigger, come from a Signal Editor block, you do not require a Rate transition block. The inputs have the same rate.

Using Trigger Signals as Clocks

You can use a trigger signal as a clock in your HDL code by using the Use trigger signal as clock configuration parameter for the triggered subsystems. You can use this setting to partition your design into different clock regions in the generated code. You can model:

A design with clocks that run at the same rate, but out of phase

Clock regions driven by an external or internal clock divider

Clock regions driven by clocks whose rates are not integer multiples of each other

Internally generated clocks

Clock gating for low-power design

For examples, see Use Trigger Signal As a Clock in a Triggered Subsystem and Generate Multiple Clocks Using Trigger As Clock.

Enable Trigger Signal as Clock Setting

To use a trigger signal as a clock, use one of these approaches:

In the Configuration Parameters dialog box, click the HDL Code Generation > Global Settings pane. In the Ports tab, select Use trigger signal as clock.

Set the

TriggerAsClockproperty by usingmakehdlorhdlset_param. For example, to generate HDL code that uses the trigger signal as clock for triggered subsystems in a DUT subsystem namedmyDUTin a model namedmyModel, enter:makehdl ("myModel/myDUT",TriggerAsClock="on")

The Clock edge model configuration parameter must match the Trigger type of the Trigger block inside the triggered subsystem.

Note

Using a trigger as the clock for triggered subsystems can result in timing mismatches of one cycle during test bench simulation.

Use Trigger Signal As a Clock in a Triggered Subsystem

This example shows how to use the trigger port of a Triggered Subsystem block as a clock signal in your generated HDL code.

The model TriggerAsClockSingle has a DUT subsystem that contains a Triggered Subsystem block. Load and open the TriggerAsClockSingle model.

load_system("TriggerAsClockSingle"); set_param("TriggerAsClockSingle",'SimulationCommand','Update') open_system("TriggerAsClockSingle/DUT");

To use the trigger signal as a clock in your generated HDL code, in the Configuration Settings dialog box, click the HDL Code Generation > Global Settings pane. In the Ports tab, Use trigger signal as clock. Then, generate the HDL code for the DUT subsystem by using the makehdl command:

makehdl("TriggerAsClockSingle/DUT")

In the generated HDL code, HDL Coder maps the trigger port of the Triggered Subsystem to the clock. This code snippet shows the HDL code of triggered subsystem which uses the Trigger signal as a clock.

Delay1_process : PROCESS (Trigger, reset)

BEGIN

IF reset = '1' THEN

Delay1_out1 <= to_unsigned(16#0000#, 16);

ELSIF Trigger'EVENT AND Trigger = '1' THEN

Delay1_out1 <= Gain_out1;

END IF;

END PROCESS Delay1_process;Use a Trigger as a Clock Without Synchronous Registers

When you use a trigger as a clock in a triggered subsystem, each triggered

subsystem input or output requires synchronization delays immediately outside

and immediately inside the subsystem. These delays act as a synchronization

interface between the regions running at different rates. HDL Coder™ allows you to generate HDL code without adding the synchronization

delays by enabling the TriggerAsClockWithoutSyncRegisters

option. By default, this option is on.

Using Triggered Subsystems with Resettable Subsystems

You can model control signals, such as clock and reset signals, by using triggered and resettable subsystems. You can use the triggered subsystem to model the trigger port as a clock and use a resettable subsystem to model the reset port from Simulink.

When you generate code from a model that contains triggered and resettable subsystems, you can:

Generate code that has a single clock and reset for a nested resettable subsystem inside a triggered subsystem by using the Use trigger signal as clock and Minimize global resets parameters.

Generate code that has multiple clock and reset signals for a model that contain multiple triggered and resettable subsystems. See Generate Multiple Clocks and Resets Using Triggered and Resettable Subsystems.

Model a Unit Delay Resettable Synchronous block in the triggered subsystem by adding the Unit Delay block to a resettable subsystem with synchronous semantics and placing the resettable subsystem inside triggered subsystem.

Model a Unit Delay Enabled Resettable Synchronous block in the triggered subsystem by adding the Unit Delay Enabled block to a resettable subsystem with synchronous semantics and placing the resettable subsystem inside triggered subsystem.

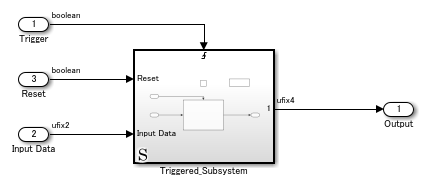

Model a Single Clock and Reset Signal by Using Triggered and Resettable Subsystems

This example shows how to model clock and reset signals by using triggered and resettable subsystems.

The model ClockAndResetModellingUsingTriggerAsClock has a DUT subsystem that contains a triggered subsystem. Load and open the ClockAndResetModellingUsingTriggerAsClock model.

load_system("ClockAndResetModellingUsingTriggerAsClock"); set_param("ClockAndResetModellingUsingTriggerAsClock",'SimulationCommand','Update') open_system("ClockAndResetModellingUsingTriggerAsClock/DUT");

The triggered subsystem contains a resettable subsystem. You can use a resettable subsystem to model a reset port for your model. To ensure that the model contains a single reset signal from the resettable subsystem, minimize the global resets in the model. In the Configuration Parameters dialog box, click the HDL Code Generation > Global Settings pane. In the Ports tab, enable Minimize global resets.

To use a trigger signal as a clock in your generated HDL code, select the Use trigger signal as clock parameter in the Ports tab. Then, generate the HDL code for DUT subsystem by using makehdl command:

makehdl("ClockAndResetModellingUsingTriggerAsClock/DUT")

In the generated HDL code, HDL Coder maps the trigger port of the triggered subsystem to the clock and reset signal from the resettable subsystem. The HDL code of the triggered subsystem shows the mapping of the trigger port to the clock signal in the resettable subsystem.

module Triggered_Subsystem

(Trigger,

Reset_1,

Input_Data,

Output_rsvd); input Trigger;

input Reset_1;

input [1:0] Input_Data; // ufix2

output [3:0] Output_rsvd; // ufix4wire [3:0] Resettable_Subsystem_out1; // ufix4

Resettable_Subsystem u_Resettable_Subsystem (.clk(Trigger),

.Input_Data(Input_Data), // ufix2

.Reset_1(Reset_1),

.Output_rsvd(Resettable_Subsystem_out1) // ufix4

);

assign Output_rsvd = Resettable_Subsystem_out1;endmodule // Triggered_Subsystem

Limitations

HDL Coder supports HDL code generation for triggered subsystems that meet these conditions:

The subsystem is not both triggered and enabled.

The trigger signal is a scalar.

If the output of the subsystem is a bus, the initial value of the outport must be 0.

All inputs and outputs of the triggered subsystem, including the trigger signal run at the same rate.

In the Trigger block, Show output port parameter is cleared.

In the Inport block inside the triggered subsystem, the Latch input by delaying outside signal check box is cleared.

If the DUT contains these blocks, RAMArchitecture HDL block property is set to

WithClockEnable:Dual Port RAM

Simple Dual Port RAM

Single Port RAM

If you enable the Use trigger signal as clock model configuration parameter, the triggered subsystem cannot contain a PN Sequence Generator block.

The triggered subsystem cannot contain these blocks:

Discrete-Time Integrator

CIC Decimation

CIC Interpolation

FIR Decimation

FIR Interpolation

Downsample

Upsample

HDL Cosimulation

Rate Transition

Pixel Stream FIFO

See Also

Use trigger signal as clock | Triggered Subsystem