时钟与多速率设计

为具有单个或多个时钟及时钟控制元素(如时钟复位和时序控制器)的多速率模型生成 HDL 代码。

主题

- Generate a Global Oversampling Clock

Generate a global oversampling clock to integrate your DUT into a larger design.

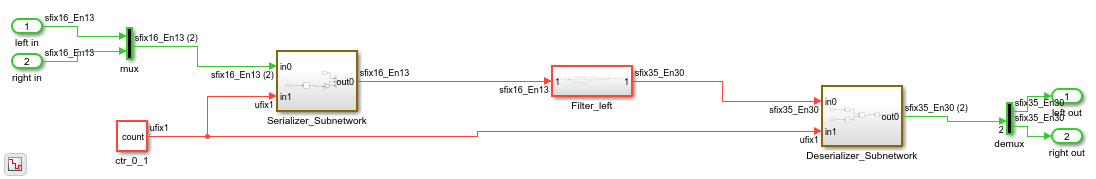

- Code Generation from Multirate Models

Overview of HDL code generation for single-clock, single-tasking multirate models.

- Multirate Model Requirements for HDL Code Generation

Guidelines for setting up multirate models and blocks for HDL code generation.

- Timing Controller for Multirate Models

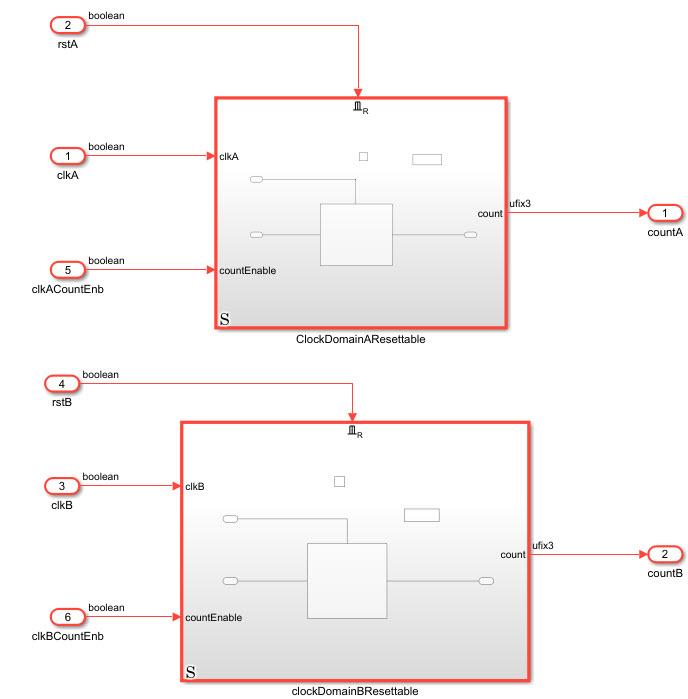

Learn about timing controllers and clock enables in a multirate model.

- Generate Reset for Timing Controller

How to generate reset for timing controller.

- Use Triggered Subsystem in HDL Code Generation

Best practices for using Triggered Subsystems, Trigger As Clock setting in HDL code generation.

- Use Triggered Subsystem for Asynchronous Clock Domain

Design a model for an asynchronous clock domains using triggered subsystems.

- Generate Clock Enable Signals

Generation of clock enable signals in your DUT for single rate and multirate models.