Demux

提取并输出虚拟向量信号的元素

库:

Simulink /

Commonly Used Blocks

Simulink /

Signal Routing

HDL Coder /

Commonly Used Blocks

HDL Coder /

Signal Routing

描述

Demux 模块提取输入向量信号的分量,再将它们输出为单独的信号。输出信号端口从上到下排列。

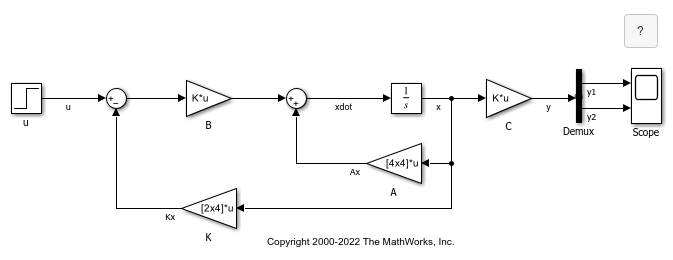

示例

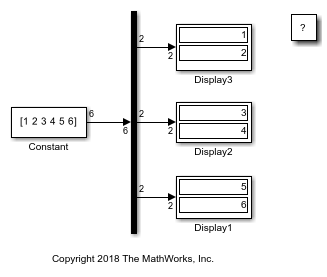

您可以使用 Demux 模块将输入信号均匀分布在所需数量的输出上。对于长度为 6 的输入向量,当您将输出数目参数设置为 3 时,Demux 模块会创建三个输出信号,每个信号的大小为 2。

要查看此行为,请打开并仿真示例模型。

mdl = "DemuxVectorUnspecified";

open_system(mdl)

sim(mdl);

当使用 Demux 模块从向量输入中提取和输出元素时,可以在向量表达式中使用 -1 来指示该模块动态调整对应端口的大小。当向量表达式同时包含正值和 -1 值时,该模块会根据需要将尽可能多的元素分配给具有正值的端口。该模块会尽可能将其余元素均匀地分布在值为 -1 的端口上。

在此示例中,Demux 模块的输出数目参数设置为 [-1, 3, -1]。因此,该模块输出三个信号,其中第二个信号始终具有三个元素。第一和第三个信号的大小取决于输入信号的大小。对于具有七个元素的输入向量,Demux 模块在第一个端口输出两个元素,在第二个端口输出三个元素,在第三个端口输出两个元素。

要查看此行为,请打开并仿真示例模型。

mdl = "DemuxVectorSpecified";

open_system(mdl)

sim(mdl);

扩展示例

端口

输入

Demux 模块从中选择标量信号或更小向量的向量输入信号。

数据类型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | image

输出

输出从输入向量中提取的信号。输出信号端口从上到下排列。有关各种模块方向的端口顺序的描述,请参阅标识旋转或翻转模块上的端口位置。

数据类型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated | image

参数

指定输出数目以及每个输出端口的维度(可选)。

值可以是指定输出数目的标量,也可以是通过元素指定模块输出端口宽度的向量。模块根据输入信号的大小以及输出数目参数的值来确定输出的大小。

如果您为输出数目参数指定了标量,而所有输出端口都已连接,则当您在靠近 Demux 模块输出端的位置绘制新的信号线时,软件会添加一个端口并更新输出数目参数。

对于宽度为 n 的输入向量,下表描述模块输出的内容。

| 参数值 | 模块输出 | 示例和注释 |

|---|---|---|

|

| 如果输入是一个三元素向量,而您指定了三个输出,则模块将输出三个标量信号。 |

| 错误 | 不支持此值。 |

|

| 如果输入是一个六元素向量,而您指定了三个输出,则模块将输出三个二元素向量。 |

|

| 如果输入是一个五元素向量,而您指定了三个输出,则模块将输出两个二元素向量信号和一个标量信号。 |

|

| 如果输入是一个五元素向量,而您指定了 |

一个数组,其中的一个或多个 例如,假设您有一个四元素数组,总宽度为 14,您将参数指定为 那么第三个元素( |

| 如果 |

| 错误 | 不支持此值。 |

如果您指定的输出数目少于输入元素的数目,则模块会尽可能将这些元素均匀地分配给各个输出。

不支持指定非双精度值,例如 single(3)。

编程用法

要以编程方式设置模块参数值,请使用 set_param 函数。

| 参数: | Outputs |

| 值: | '2' (默认) | scalar in quotes | vector in quotes |

| 数据类型: | char | string |

示例: set_param(gcb,'Outputs','4')

默认情况下,模块图标是一个填充了模块前景颜色的实心条形。要将图标显示为一个包含模块类型名称的框,请选择无。

编程用法

要以编程方式设置模块参数值,请使用 set_param 函数。

| 参数: | DisplayOption |

| 值: | 'bar' (默认) | 'none' |

示例: set_param(gcb,'DisplayOption','none')

模块特性

数据类型 |

|

直接馈通 |

|

多维信号 |

|

可变大小信号 |

|

过零检测 |

|

扩展功能

实际数据类型或功能支持取决于模块实现。

HDL Coder™ 提供影响 HDL 实现和综合逻辑的额外配置选项。

此模块具有一个默认 HDL 架构。

| ConstrainedOutputPipeline | 通过移动设计中现有延迟的方式来放置在输出端的寄存器的数量。分布式流水线不会重新分发这些寄存器。默认值为 |

| InputPipeline | 要在生成的代码中插入的输入流水线阶段数。分布式流水线和受限输出流水线可以移动这些寄存器。默认值为 |

| OutputPipeline | 要在生成的代码中插入的输出流水线阶段数。分布式流水线和受限输出流水线可以移动这些寄存器。默认值为 |

| SynthesisAttributes | 指定模型中模块和模块输出信号的综合属性。生成的 HDL 代码包含这些属性。有关详细信息,请参阅SynthesisAttributes (HDL Coder)。 |

此模块支持复信号的代码生成。

PLC 代码生成

使用 Simulink® PLC Coder™ 生成结构化文本代码。

实际数据类型或功能支持取决于模块实现。

版本历史记录

在 R2006a 之前推出使用 SynthesisAttributes HDL 模块属性指定模块及其输出信号的综合属性。HDL Coder 在生成的 HDL 代码中包含这些属性。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)