SoC Blockset Model Structure

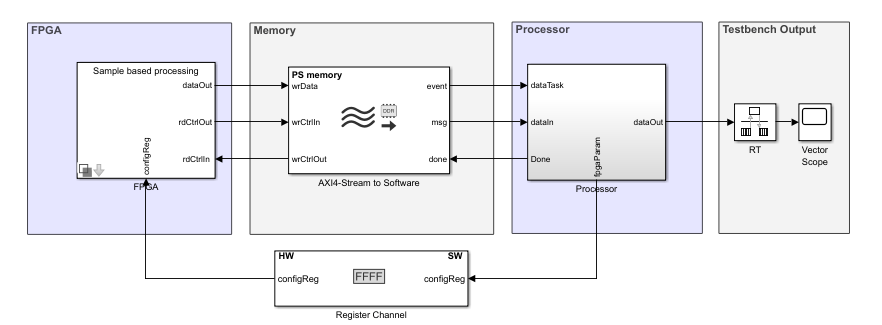

An SoC Blockset™ model consists of a top model that includes at least one of these reference models.

An FPGA reference model represents the FPGA part of an SoC device. The top model can include at most one FPGA reference model. For information on how to set up an FPGA reference model, see User Logic on FPGA.

A processor reference model represents the processor part of an SoC device. The top model can include one or more processor reference models. For information on how to set up a processor reference model, see Software and Task Management on Processor.

The processor and the FPGA subsystems communicate through a Memory Channel, Register Channel or Interrupt Channel block.

Note

You must set the Processing Unit parameter in each model and referenced model.

Open the Hardware Settings on the Hardware Implementation pane.

In the top model, set the Processing Unit parameter to

None.In the FPGA model, set the Processing Unit parameter to

FPGA.In the processor model, set the Processing Unit parameter to

APU.

In addition to FPGA and processor reference models, the top model can include additional SoC Blockset blocks, such as the blocks listed here, for modeling interfaces and test bench components.

The following image shows an SoC Blockset model, with an FPGA reference model, a processor reference model, communicating over a memory channel.

For an example of an SoC Blockset model, see Streaming Data from Hardware to Software.

SoC Blockset provides project templates for common SoC use-cases. Use them as a starting point for your design.