ePWM 4 型时基同步概述

时基时钟同步

外设时钟使能寄存器中的 TBCLKSYNC 位允许所有用户将所有已启用的 ePWM 模块全局同步到时基时钟 (TBCLK)。设置后,所有启用的 ePWM 模块时钟都将与 TBCLK 的第一个上升沿对齐并开始运行。这是 ePWM 模块的默认设置。

时基计数器外围设备同步

每个 ePWM 模块都有一个外围同步输出 (SYNCPER)。该输出信号用于将 CMPSS 与 EPWM 同步。

该信号的来源可以在 ePWM 模块中配置,如下所示:

相应的信号可以与 CMPSS 一起使用,使用 硬件实现 > Target hardware resources > CMPSS 下的 EPWM peripheral synchronization event 参数。

时基计数器同步

时基计数器同步可以提高 ePWM 模块同步的灵活性。时钟同步方案允许 ePWM 模块在需要时作为一个单一系统运行。此外,这种同步方案还可以扩展到捕获外围子模块 (eCAP)。在第 4 类 ePWM 中,有两种时基计数器同步方案可供选择。

ePWM 中的时基计数器同步选项

在处理器 F2837x、F2807x 和 F28004x 中,ePWM 模块按如下方式串联在一起。

在处理器 F2838x、F28002x 和 F28003x 中,没有固定的同步信号链,但每个 ePWM 或 eCAP 模块都可以配置为使用或忽略同步输入,并且可以作为同步信号的源,即任何 ePWM 或 eCAP 都可以与任何其他 ePWM 或 eCAP 同步。

当 TBCTL 中的 PHSEN 位被置位时,当发生下列条件之一时,ePWM 模块的时基计数器 (TBCTR) 将自动加载相位寄存器 (TBPHS) 的内容:

EPWMxSYNCI/Synchronization Input Pulse- 当检测到输入同步脉冲时,相位寄存器的值被加载到计数器寄存器中(TBPHS→TBCTR)。此操作在下一个有效的时基时钟 (TBCLK) 边沿发生。Software Forced Synchronization Pulse- 向 TBCTL 中的SWFSYNC控制位写入 1 会触发软件强制同步。该脉冲与同步输入信号为 ORed,因此与EPWMxSYNCI上的脉冲具有相同的效果。Digital Compare Event Synchronization Pulse-DCAEVT1和DCBEVT1数字比较事件可以配置为生成同步脉冲,其效果与EPWMxSYNCI相同。在加减计数模式下,

TBCTL寄存器中的PSHDIR位在同步事件发生后立即配置时基计数器的方向。新方向与同步事件发生之前的方向无关。在向上计数或向下计数模式下,PHSDIR位将被忽略。

这些选项在 ePWM 模块中设置,如下所示。

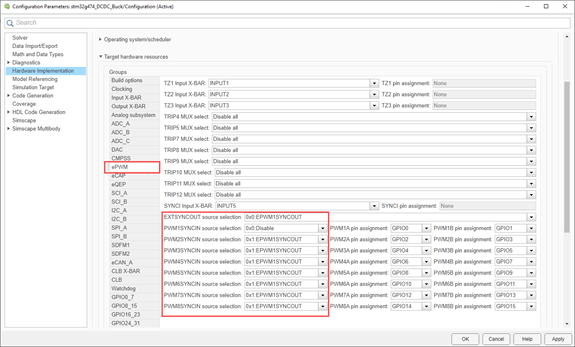

如图所示,可以在 硬件实现 > Target hardware resources > ePWM 下选择 EXTSYNCOUT 和 EPWMSYNCI 信号的来源。

注意

EXTSYNCOUT和EPWMSYNCI参数因处理器而异。对于处理器 F28004x/F2837xD/F2837xS/F2807x,EXTSYNCIN1 和 EXTSYNCIN2 分别映射到输入 X-BAR 5 和输入 X-BAR 6。

对于 F2838x/F28003x/F28002x 处理器,在没有 ePWM 模块的模型中,可以使用 EXTSYNCOUT 选项从 eCAP 发送同步输出。

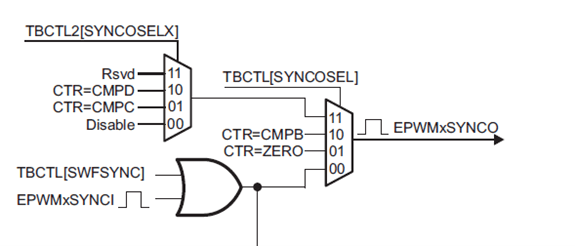

EPWMxSYNCO 信号是输出脉冲,用于同步其他 ePWM 模块的计数器。对于处理器 F2837x/F2807x 和 F28004x,可以生成如下图所示的 EPWMxSYNCO 信号。

对于处理器 F2838x、F28002x 和 F28003x,EPWMxSYNCO 信号可以在多种条件下生成,如下所示。

注意

目前不支持配置单次同步模式。

EPWMxSYNCO 可以在 ePWM 模块中按如下所示进行配置。

适用于 F2837x/07x/004x 处理器。

适用于 F2838x/002x 和 003x 处理器。

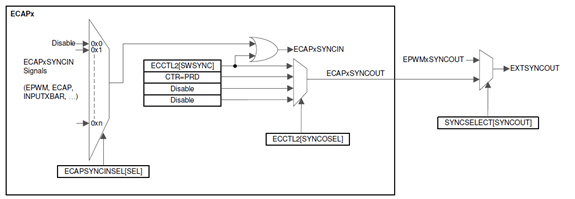

eCAP 中的时基计数器同步选项

eCAP 模块可以通过选择一个共同的 SYNCIN 源来相互同步。eCAP 的 SYNCIN 源可以是软件同步输入,也可以是外部同步输入。外部同步输入信号可以来自 eCAP、X-Bar 或 EPWM。

当 CTR=PRD 时,来自 eCAP 的 SYNCOUT 信号可以传递或生成。

虽然 eCAP 在 eCAP 和 APWM 模式下均可实现同步,但 SYNCOUT 信号的 CTR=PRD 源仅在 eCAP 处于 APWM 模式时有效。

可以在 eCAP 模块中选择相位偏移、软件同步输入和同步输出选项,如下所示。

可以在配置参数的 eCAP 选项选项卡中选择 eCAP SYNCIN 信号。确保在 eCAP 模块中启用 Enable counter Sync-In mode,同步输入才能生效。