How to Generate a 5G Waveform for SystemVerilog Verification Using 5G Toolbox

One of the challenges in RTL verification is developing realistic directed tests. New standards like the 3GPP 5G New Radio (NR) standard require deep domain expertise, making it even more challenging to create a standard-compliant waveform verification model.

5G Toolbox™ provides standard-compliant functions and examples for the modeling, simulation, and verification of 5G communications systems to ensure they comply with the 5G NR standard. This video shows how to use HDL Verifier™ to automatically generate a SystemVerilog verification component from a 5G Toolbox function that synthesizes a realistic waveform with parameters you can adjust in SystemVerilog, along with some of the more common steps you will go through in the process, including:

- Partitioning the MATLAB® test bench from the algorithm and defining what is parameterizable

- Converting the MATLAB function output to fixed point

- Addressing coding style issues that prevent C code generation

- Integrating the generated SystemVerilog DPI component into a simple test bench

Published: 6 Mar 2020

If you’re designing hardware for a 5G wireless application, you need to verify that the hardware functions according to the standard. How do you create standard-compliant waveforms, and even better, how do you create them with parameters to test different scenarios?

MATLAB with 5G Toolbox provides standard-compliant functions and examples for the modeling, simulation, and verification of 5G communications systems to ensure they comply with the 3GPP 5G New Radio (NR) standard.

Here I will show how to reuse what the comms algorithm engineers develop to generate a 5G New Radio waveform for SystemVerilog verification. How long would it take to learn the 5G spec and code up waveforms in SystemVerilog?

5G Toolbox has some nice examples of waveform generation that you can use to get started, like this one here. But often in algorithm development, the tests and the algorithm are not partitioned from each other.

Wireless HDL Toolbox contains 5G hardware design IP, with test benches that use this 5G Toolbox functionality and are already structured for this, like the NR HDL Cell Search reference. This design searches for the strongest cell ID, which means it performs OFDM demodulation and identifies the strongest primary and secondary synchronization signals.

The bulk of the waveform generation is done in this function, which generates block pattern case B. The test bench adds in a frequency offset and noise to make it more representative of what you’d be receiving over the air. I’m going to put that functionality into the main function and pass these parameters as inputs, so when I use the component in SystemVerilog I can use the same stimulus and sweep the parameters for signal-to-noise ratio, frequency offset, and set a different cell ID. This is hard-coded for case B, I could parameterize that too—but I’m keeping this simple for now.

Here’s the end of the main function, where I added the frequency offset and noise. The other thing I do is convert it to fixed-point. The default type in MATLAB is double-precision floating-point, but the RTL design’s inputs are fixed-point.

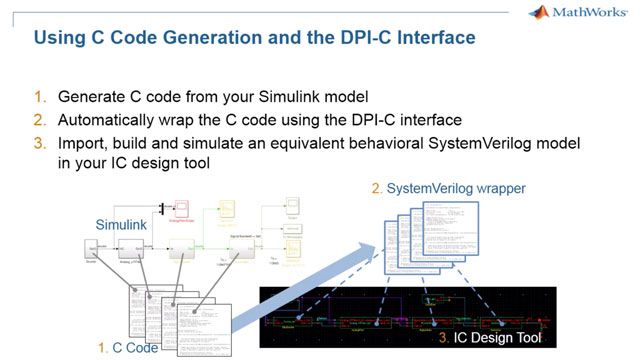

HDL Verifier is the product that generates this component. It calls MATLAB Coder to generate C code, and builds everything to link it into a SystemVerilog simulation. So it will run natively in any SystemVerilog simulator.

The command is dpigen, and I need to define the data types for the input parameters—it can figure out the outputs from the code that drives them.

But as I start to run this command, I get some errors. MATLAB is an interpreted language that’s pretty forgiving on data types, so I had to make some fixes for C code generation, for instance if a variable is going to be assigned complex data, initialize it with complex data. And C code generation doesn’t allow you to add elements to a structure after you start reading from it, so there are a few fixes for that. But overall these edits were pretty minor.

Now I can generate the component, and take a look at what gets created. It generates all the C code necessary to build the function, the makefile to build it, and it builds the DLL. If you need to compile on a different platform, you can use the makefile. It also generates some SystemVerilog code to show how to use the component.

It needs to initialize the handle, it has reset behavior, and when enabled, it calls the function every posedge of the clock. For this case, notice that the function outputs the entire waveform—that’s how MATLAB code typically works—but it means I probably don’t want to call this over and over, I’m only going to call it once then disable it.

I created a simple test bench, nothing fancy here at all. It just instantiates the RTL design, which again is generated from the Wireless HDL Toolbox IP. Then here I just instantiate that generated SystemVerilog DPI. This is a really simple test bench—it just does a reset, sets some parameters for the DUT, then loads in the waveform. Here is where it disables the DPI after one call. Then it loops through and pulls out a sample at a time from the full waveform.

You can also have the MATLAB and the C code generate samples on the fly if you want to use less memory and are ok with slightly longer run times.

I’ve already compiled the DUT, this is the DO file for my little testbench. The key here is that I need to also be sure to compile the generated SystemVerilog and link in the DLL when starting the simulator.

This takes a while to simulate, so I’ll skip ahead to the waves. The input signals are up here, the waveform parameters and the data itself. In this design the hardware gets called in two passes, I’m just running the first pass, which is searching for PSS detection. This reportValid indicates where a PSS correlation was detected, and if I zoom in on one of these, there’s the correlation result, it cleared the threshold, and it’s PSS0.

You can also generate a checking component from MATLAB or Simulink, and you can even generate UVM from Simulink. But here I just wanted to focus on the waveform.

Overall this took about an hour or two of work, and it probably would have been even quicker if I had collaborated live with the developer of the MATLAB code. But this is a really quick and efficient way to generate parameterizable SystemVerilog components to generate 5G New Radio standard-compliant waveforms to verify your 5G hardware designs.