Infineon AURIX 的多核架构

为 Infineon® AURIX™ TC3x 微控制器的多核模型设计、仿真和生成代码

Infineon AURIX TC3x 系列中的微控制器最多可包含六个 TriCore® 处理单元(TriCore 0 至 TriCore 5)。TriCore 0 是主要处理单元,负责处理 AURIX 微控制器中的系统初始化、启动过程和关键控制任务。这些处理单元可以独立或协作运行。您可以将不同应用程序分配给各个处理单元。为了支持 Simulink® 中的模块化和并发设计,您可以将一个复杂应用程序的各个组件分布在多个处理单元上。

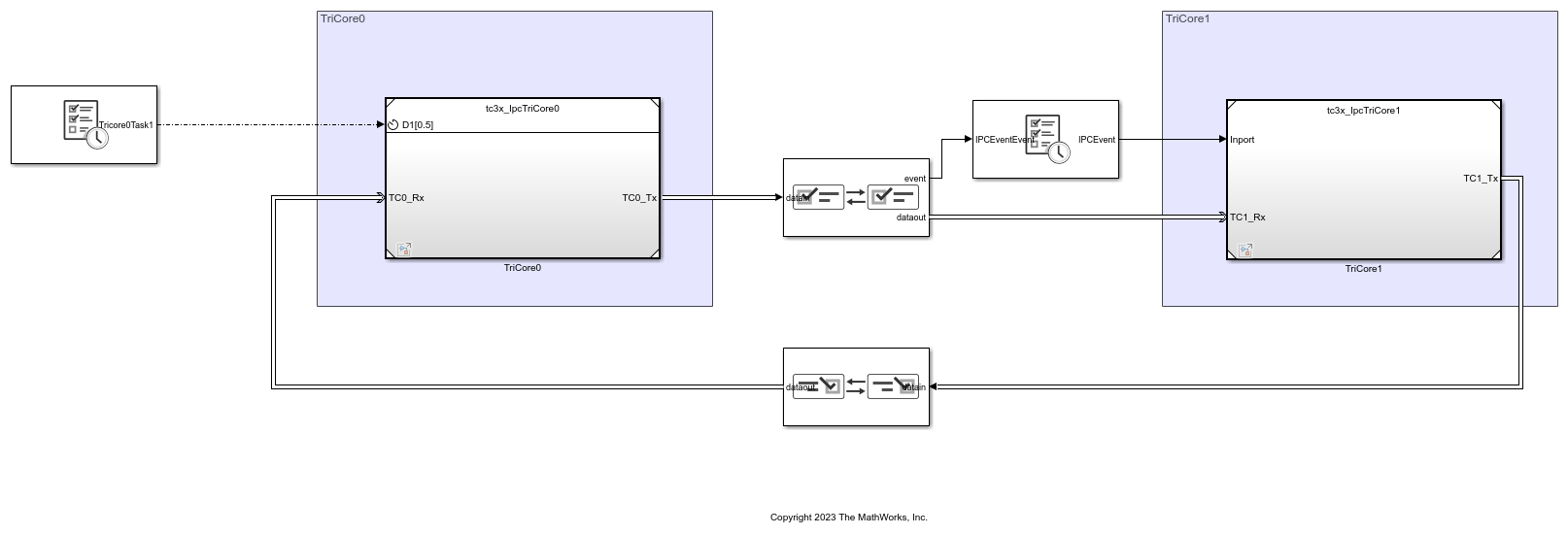

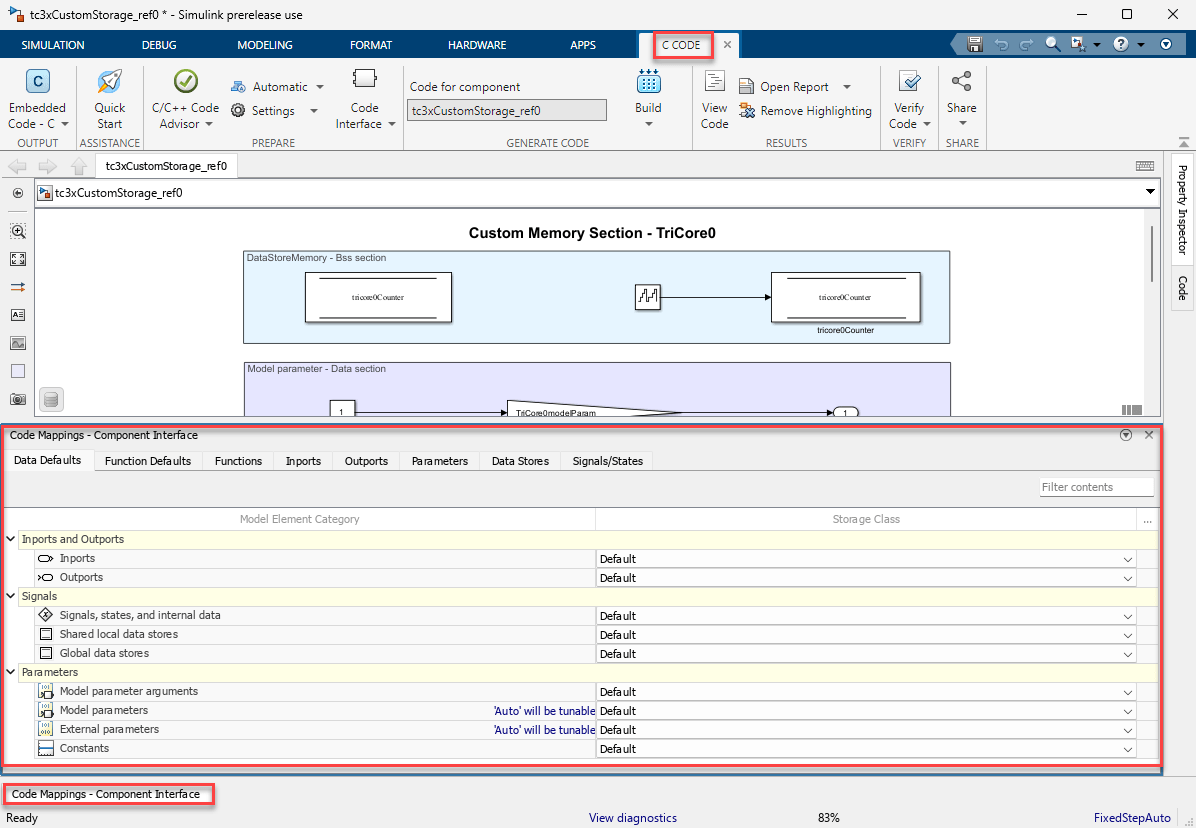

Embedded Coder® Support Package for Infineon AURIX TC3x Microcontrollers 可帮助您设计多核和单核应用程序模型。下图显示使用 Infineon AURIX TC4x 微控制器的不同处理单元的推荐建模方案。

下图显示使用 Infineon AURIX TC3x 微控制器的不同处理单元 (PU) 的推荐建模方案。

一体式模型 - 单一或独立 Simulink 模型,它生成一个集成的应用程序,该应用程序由 Simulink 在单个处理单元上执行。

基于 SoC 的多核模型 - 统一的片上系统 (SoC) 架构,它为参与的处理单元生成一个或多个集成应用程序。SoC 模型由一个顶层模型和两个或多个独特的引用模型组成。顶层模型表示整个嵌入式系统,其中包含在引用模型上运行的应用程序算法或模型。

模块

工具

主题

建模

- SoC-Based Multicore Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement multicore SoC models. - SoC-Based Multicore Modeling Workflow for Infineon AURIX Microcontrollers

Create SoC based multicore models.

- Monolithic Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement single-core models.

代码生成

- Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool. - Generate Software Executables for Multicore Models

Generate single or multiple ELF files for all participating cores of Infineon AURIX.

处理器在环 (PIL) 仿真

- Model Reference PIL Simulation

Processor-in-the-Loop (PIL) simulation techniques for Infineon AURIX hardware boards.