使用 Infineon AURIX 进行多核仿真和优化代码生成

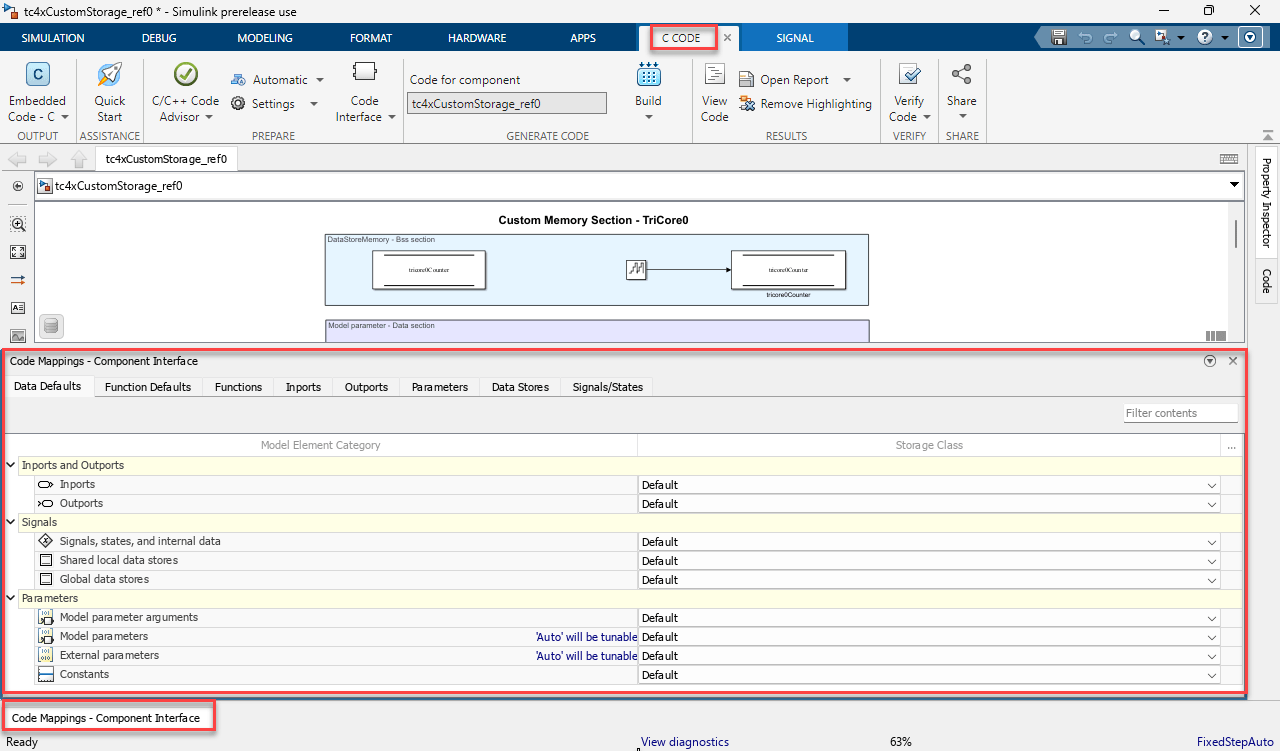

Infineon AURIX TC4x 微控制器包含 6 个同构 TriCore® CPU(TriCore 0 到 TriCore 5)和一个异构并行处理单元 (PPU)。您可以在可用的核上运行不同的模型,也可以对复杂模型进行分区以便在多个核上同时运行,从而实现设计模块化。Interprocess Data Channel 模块处理多个核之间的通信。在对多核模型进行仿真后,您可以使用 SoC 构建器工具在 Infineon AURIX TC4x 硬件板上部署生成的代码,并使用 Infineon 的 One Eye 工具监控来自硬件的信号。

PPU 执行计算的速度比 TriCore 快。PPU 核通过使用代码替换库将部分生成的代码替换为硬件特定的代码来提高模型的性能。TriCore 0 核是主核,它可以与所有其余辅助核(TriCore 1 到 TriCore 5 和 PPU)通信。

使用 Infineon AURIX 微控制器的多个核创建一个 SoC 模型后,请使用 SoC 构建器生成可执行文件、代码和对硬件板进行编程。请参阅Getting Started with Multicore Modeling and Targeting for Infineon AURIX TC4x Microcontrollers示例,了解如何验证、编译和运行多核模型,以生成可执行文件、代码和对 Infineon AURIX TC4x 硬件板进行编程。

模块

工具

主题

- Parallel Processing Unit for Optimized Code Generation

Use PPU to implement models with large data processing requirements or fast execution time requirements.

- PIL Simulation Using nSIM Simulator

Run PIL simulations and test PPU based application models using nSIM simulator.

- Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool.

- Generate Software Executables for Multicore Models

Generate ELF file for all participating homogenous cores of Infineon AURIX.

- Task Duration

Set the execution time or duration of a task in Task Manager block.

- What is Task Execution?

Learn the definition of task execution and task life-cycle in a processor.

- Task Execution Playback Using Recorded Data

Replay task execution timing using recorded task timing data from previous simulations or processors.