Parallel Processing Unit for Optimized Code Generation

The parallel processing unit (PPU) is a specialized hardware accelerator designed to speed up highly parallel vector computations in complex models with large data processing requirements or fast execution time requirements. This core is based on single instruction, multiple data (SIMD) vector DSP architecture and uses a specialized memory called vector closely coupled memory (VCCM) to speed up vector computations. Application models using the PPU core of Infineon® AURIX™ microcontrollers store the participating data in VCCM.

You can use Digital Port Read, Digital Port Write, Encoder, PWM, TMADC, DSADC, FCC, Interprocess Data Read, Interprocess Data Write, Interprocess Data Channel, and Task Manager blocks to design multicore models using the PPU core of AURIX TC4x microcontrollers.

The PPU core speeds up the highly parallel computations by running the optimized functions generated using the code replacements (CRL) technique and reduction operations. For more information on the CRL technique, see What Is Code Replacement?. The PPU referenced model uses a function-call subsystem that uses CRL functionality to replace parts of generated code with hardware-specific code.

Code Replacement Library for PPU

The CRL technique optimizes the PPU run time. By default, the code generation does not contain the CRL functionality. Explore the available libraries to identify those that best meet the needs of your application.

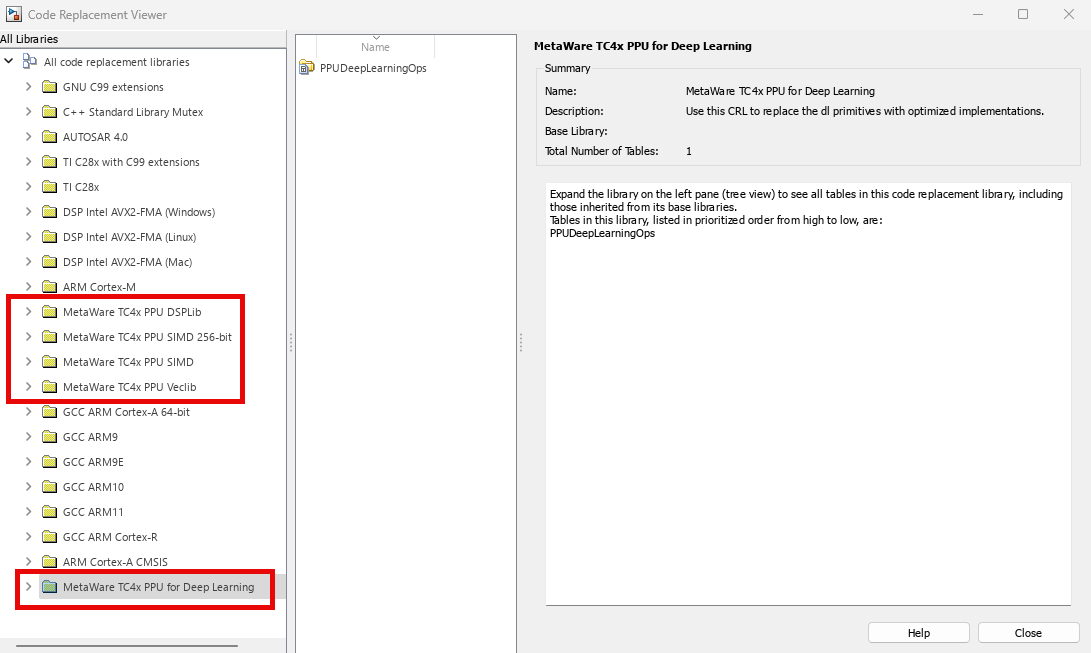

To view the available CRLs, open the Code Replacement Viewer from the

MATLAB® command window using the crviewer command. In the

left pane, select the name of a library. The viewer displays information about the library

in the right pane.

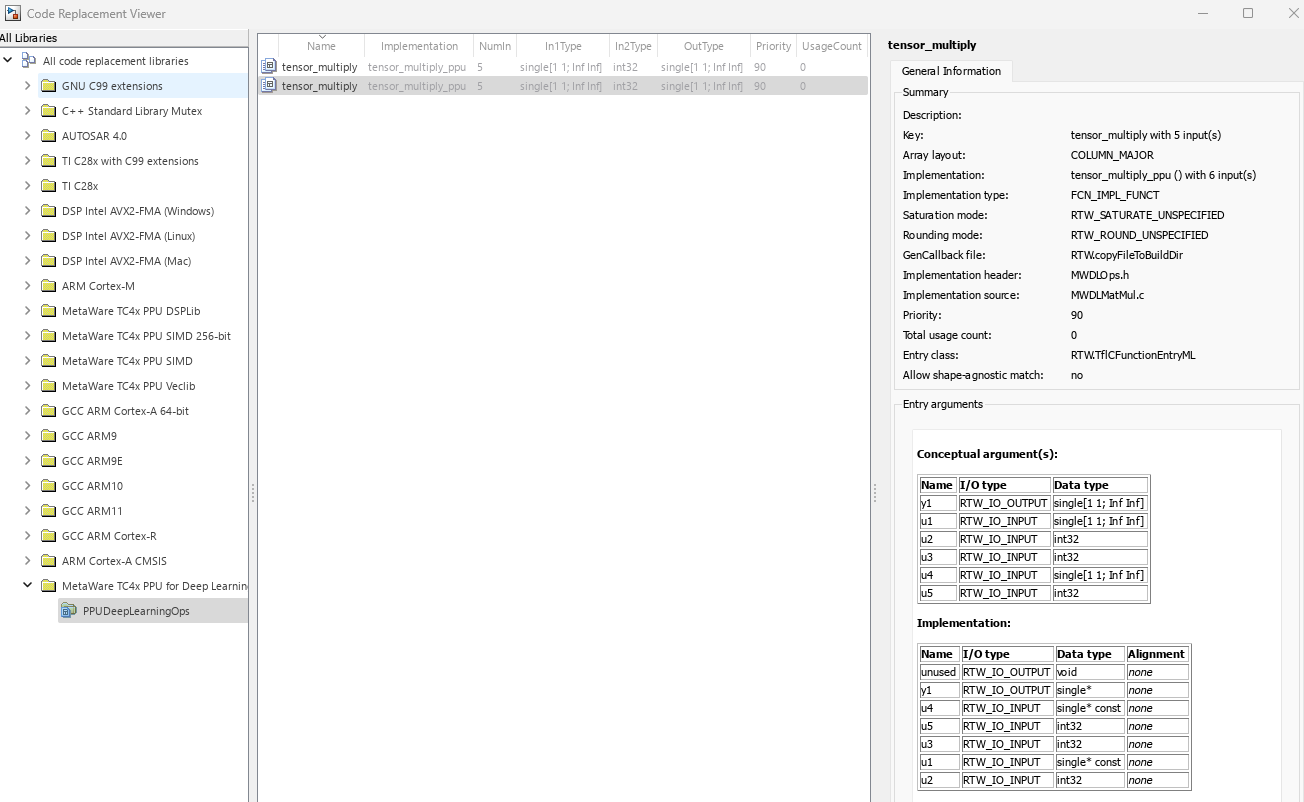

In the left pane, expand the library, explore the list of tables in the library, and select a table from the list. The middle pane displays the function and operator entries in the selected table, along with abbreviated information for each entry. In the middle pane, when you select a function or operator, the viewer displays information about that entry in the right pane.

Observe the supported data type for the available CRL entries in the middle and right panes of the code replacement viewer. Before using any CRL, ensure the data type of the application model's variables or data elements matches the required CRL entry's data type.

Select CRL and Generate Optimized Code

The PPU core supports these code replacement libraries for optimized code generation.

MetaWare TC4x PPU DSPLib — Generates function-based optimized code to perform DSP operations.

MetaWare TC4x PPU SIMD 256-bit — Generates compiler specific intrinsics-based optimized code to perform 256-bit SIMD operations on Infineon AURIX TC46x, TC49xN, and TC4Dx microcontrollers.

MetaWare TC4x PPU SIMD — Generates compiler specific intrinsics-based optimized code to perform 512-bit SIMD operations on Infineon AURIX TC49x microcontrollers.

MetaWare TC4x PPU VecLib — Generates function-based optimized code to perform linear algebra operations using basic linear algebra subprograms (BLAS ) and linear algebra package (LAPACK). For more information, see BLAS and LAPACK.

SmartCode TC4x PPU VSIMD 512-bit — Generates compiler specific intrinsics-based optimized code to perform 512-bit SIMD operations on Infineon AURIX TC49x microcontrollers.

SmartCode TC4x PPU VSIMD 256-bit — Generates compiler specific intrinsics-based optimized code to perform 256-bit SIMD operations on Infineon AURIX TC46x, TC49xN , and TC4Dx microcontrollers.

MetaWare TC4x PPU for Deep Learning — Generates function-based optimized code for DL layers, operations, and functions used in DL networks. It contains these CRL tables:

PPUDeepLearningOps— Generates function-based optimized code for these operation and functions in DL networks using Predict (Deep Learning Toolbox) block:Tensor multiplications performed in fully connected, long short-term memory (LSTM), bidirectional LSTM (BiLSTM), and gated recurrent unit (GRU) layers of deep neural networks. For more information on these layers, see List of Deep Learning Layers (Deep Learning Toolbox)

Hyperbolic tangent (tanh) and sigmoid activation functions used within recurrent neutral network layers such as LSTM, BiLSTM , and GRU layers of deep learning networks.

Tanh and sigmoid functions operating on

dlarray(Deep Learning Toolbox) objects, which you can use for custom training loops in deep learning networks.Tanh function operating on numeric array objects, which you can use for custom layers in deep learning networks.

PPUDLLayerBlocks— Generates function-based optimized code for these deep learning layer blocks used in Simulink® models.Fully Connected Layer (Deep Learning Toolbox), LSTM Layer (Deep Learning Toolbox), and ReLU Layer (Deep Learning Toolbox) blocks in deep learning networks.

Fully Connected Layer (Deep Learning Toolbox) and ReLU Layer (Deep Learning Toolbox) blocks in quantized neural networks. For more information on quantized networks, see Quantization of Deep Neural Networks (Deep Learning Toolbox) and Deep Network Quantizer (Deep Learning Toolbox).

Follow these steps to use CRL for any PPU referenced application model:

Open the Simulink model that uses a PPU core.

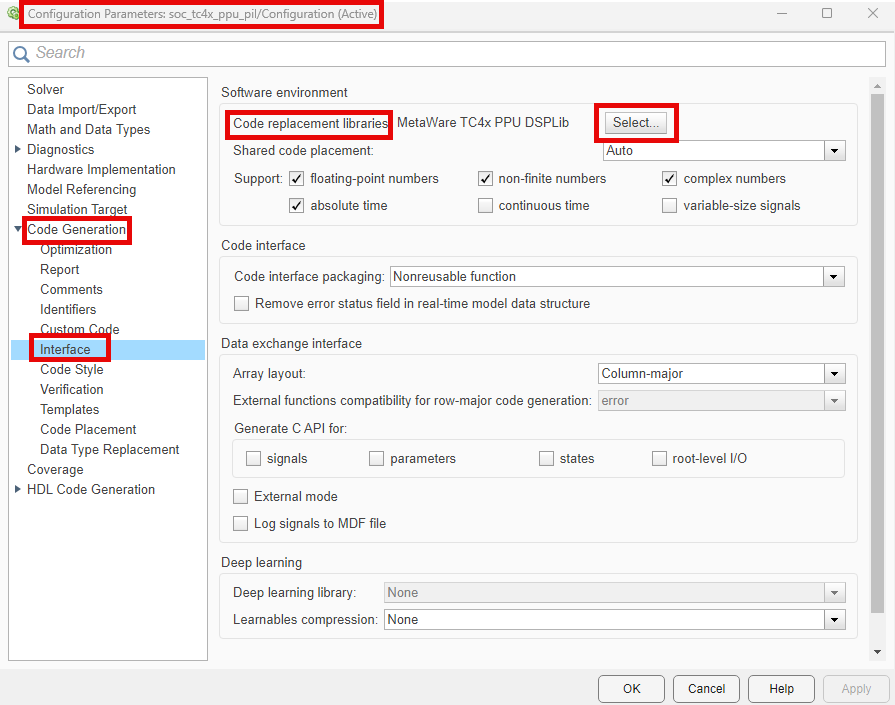

Click Ctrl+E or click Modeling > Model Settings to open the Configuration Parameters window.

Select Hardware Implementation and set the Processing Unit parameter to

PPU.

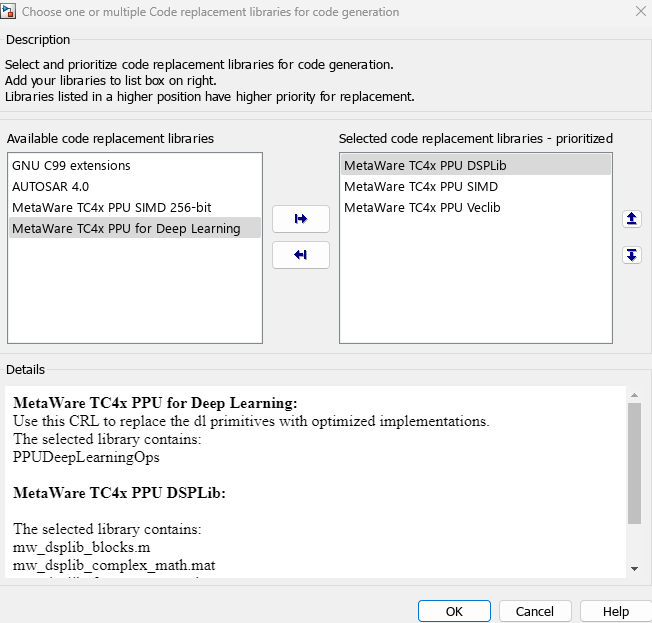

Navigate to Code Generation > Interface > Code replacement libraries and click Select to select a CRL from the libraries available for the PPU core of Infineon TC4x microcontrollers. This figure displays the CRLs available for the model in the Code Verification and Validation with PIL Using PPU example.

Use the

and

and  buttons to add and remove a CRL.

buttons to add and remove a CRL.You must choose these CRLs depending on compiler tool chain option selected in the Configuration Parameters dialog box. Navigate to Code Generation > Build process > Toolchain to view the available toolchain options.

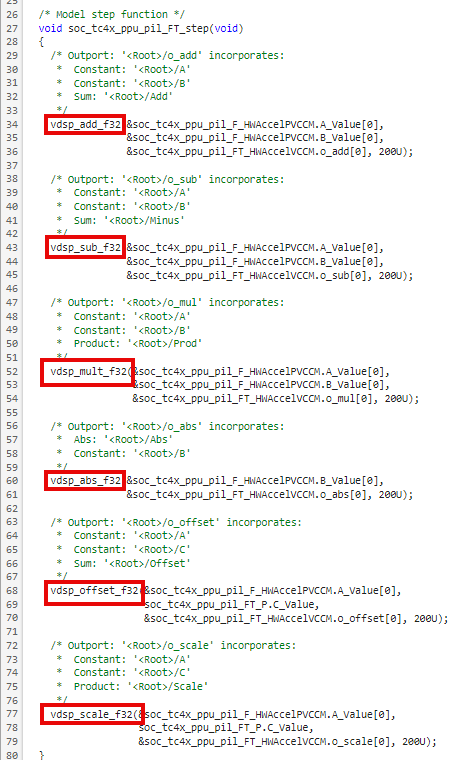

After completion of the PIL simulation steps from the Code Verification and Validation with PIL Using PPU example, this image shows the code generation report of the model with code replacements.

For PPU and TriCore based multicore models like Getting Started with PPU Accelerator for Infineon AURIX TC4x Microcontrollers, the SoC builder tool guides you through the validate, build and run procedure. Click Configure, Build, Deploy & Start on the Hardware tab of the top model to launch the SoC builder tool. Once you complete the build procedure, observe the code generation report with hardware-specific code replacements.

For application models running on the PPU core, the CRL assigns VCCM to the participating data. However, there can be a conflict with other memory section or storage class assigned to the same data elements by using the Embedded Coder Dictionary and Code Mappings Editor — C. In these cases, Simulink resolves the conflict as below:

If you assign a memory section to a specific data element and the same data element is also a designated candidate for the VCCM through the CRL, then there is a conflict and the VCCM gets highest priority. The generated code contains the hardware-specific code replacements for the functions involving that data element.

If you assign storage class to a data element and the same data element is also a designated candidate for the VCCM through CRL functionality, then there is a conflict and the storage class gets highest priority. The generated code does not contain the hardware-specific code replacements for the functions involving that data element.

Generate Optimized Code Using Reduction Operations

A reduction operation reduces a set of elements, such as an array, to a single value using an associative binary operator. For example, calculating the sum of the elements in an array is a reduction operation that uses the addition operator. For application models using PPU core, you can optimize reduction operations by generating parallel code that uses the SIMD instructions for the operation.

Follow these steps to use reduction operations for any PPU referenced application model:

Open the Simulink model that uses a PPU core.

Click Ctrl+E or click Modeling > Model Settings to open the Configuration Parameters window.

Select Hardware Implementation and set the Processing Unit parameter to

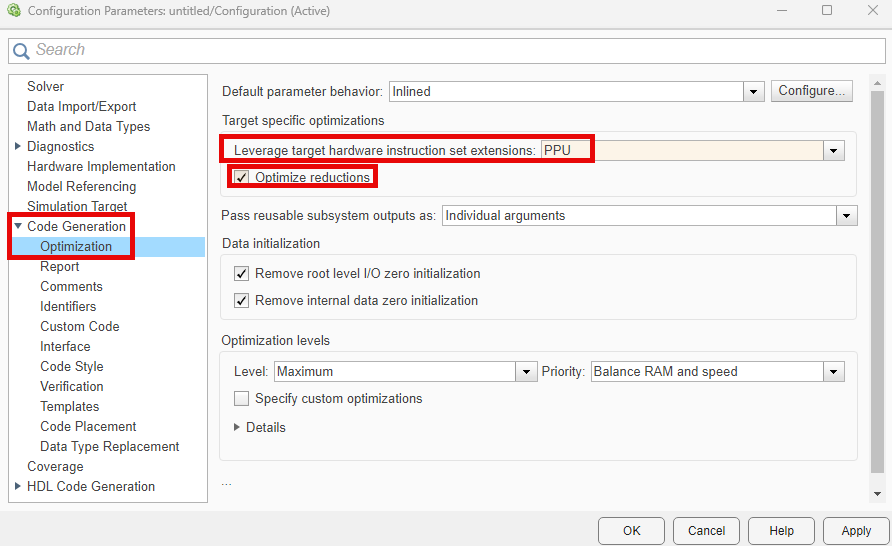

PPU.Navigate to Code Generation > Optimization, set Leverage target hardware instruction set extensions parameter to PPU, and enable Optimize reductions parameter. Click Ok.

Known Limitations

QSPI, SENT, Resolver, CDSP, MCAN Transmit, and MCAN Receive blocks are not supported with PPU.

PPU does not support external mode simulation.

PPU does not support C++ code generation.

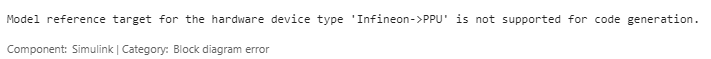

You must set the Hardware board parameter to

Infineon AURIX TC4x - TriBoardsin the Configuration Parameters window of the Simulink model. If you set Device vendor toInfineon, Device type toPPU, and select the CRL manually while keeping the Hardware board parameter set toNone, code generation fails.The PPU does not support model references, and Simulink displays an error message if you set the Processing Unit parameter to

PPUin the top-level model and the referenced model.

Optimized SIMD code replacements for reduction operations such as addition, subtraction, multiplication, and dot‑product are not supported for TC46x, TC49xN, and TC4Dx series of Infineon AURIX microcontrollers.

MetaWare TC4x PPU for Deep Learning CRL is not supported for TC46x, TC49xN, and TC4Dx series of Infineon AURIX microcontrollers.

See Also

Define Service Interfaces, Storage Classes, Memory Sections, and Function Templates for Software Architecture | SoC-Based Multicore Modeling for Infineon AURIX Microcontrollers | Monolithic Modeling for Infineon AURIX Microcontrollers | SoC Builder | Generate Code and Deploy Using SoC Builder | Generate Software Executables for Multicore Models | PIL Simulation Using nSIM Simulator

Topics

- Getting Started with PPU Accelerator for Infineon AURIX TC4x Microcontrollers

- Code Verification and Validation with PIL Using PPU

- Accelerate AI Based Software Development on Infineon AURIX TC4x Microcontroller

- Generate and Deploy Optimized Code for Digit Classification Deep Learning Network on Infineon PPU Target