Top-Level Models Using TriCores of Infineon AURIX

You can create top-level models with referenced models using TriCore processing units to implement different application models. The Analyze Sensorless Observers for Field-Oriented Control Using Multiple Cores of Infineon AURIX example includes a top-level model with two referenced models using TriCore 0 and TriCore 1 processing units. The TriCore 0 referenced model implements a sensor-based field-oriented control (FOC) technique and the TriCore 1 referenced model implements different sensorless algorithms. The example uses the auxiliary core to analyze different sensorless observers without affecting the sensor-based model running on the TriCore 0.

If you select the Processing Unit of the top-model as

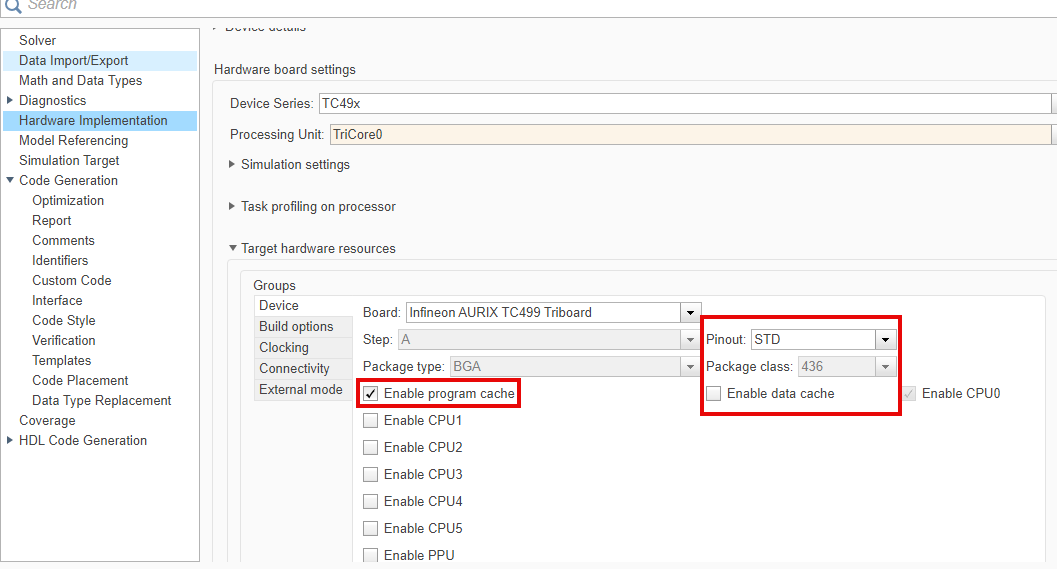

None, then the referenced models must have the same device build configuration to avoid conflict. The Package class, Pinout, Enable program cache, and Enable data cache parameters in such referenced models must match.

Every participating core of the referenced models must have information on other participating cores of the application model. If you select the Processing Unit parameter of the top-model as

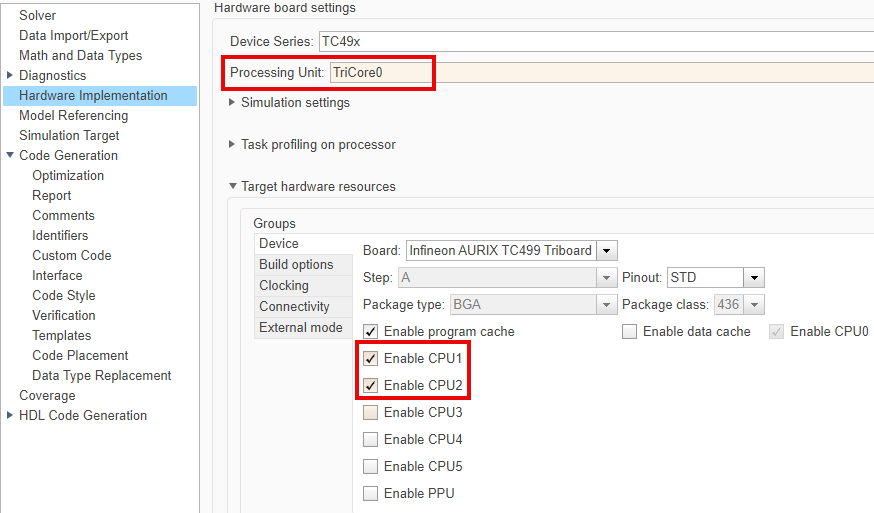

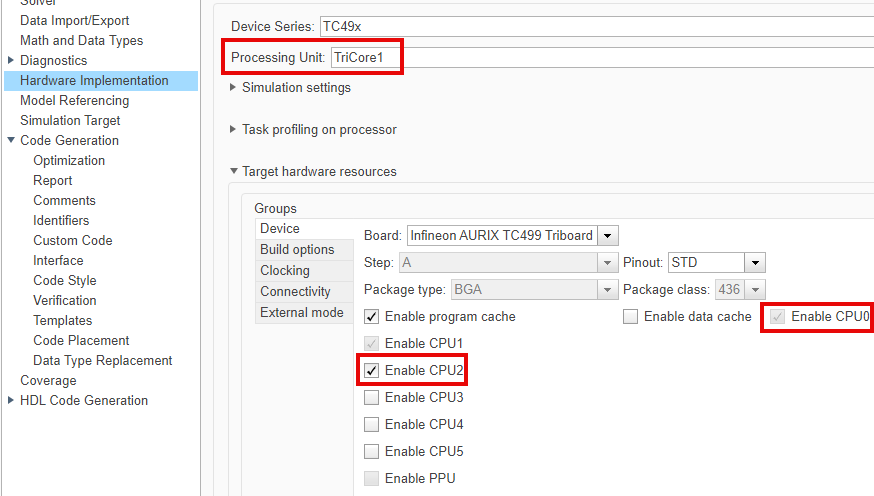

None, then Simulink® automatically configures the device settings for the top and referenced models. If you select the Processing Unit parameter of the top-model other thanNone, then you must manually set the device settings to ensure that every participating core has information about other participating cores.For example, consider a top-model with three referenced models using the TriCore 0, TriCore 1, and TriCore 2 processing units. To ensure that the TriCore 0 referenced model has information about other participating cores, select the Enable CPU 1 and Enable CPU 2 parameters in the Configuration Parameters window of the TriCore 0 referenced model.

Select the Enable CPU 2 and Enable CPU 1 parameters in the referenced models using the TriCore 1 and TriCore 2, respectively. By default, the Enable CPU 0 parameter is always selected in all the referenced models as the TriCore 0 core is the principal core.

See Also

Multicore Programming with Simulink | Concepts in Multicore Programming | Parallel Processing Unit for Optimized Code Generation | Top-Level Models Using TriCores and PPU of Infineon AURIX | Single-Core and Flat Models Using TriCore and PPU of Infineon AURIX | SoC Builder | Generate Code and Deploy Using SoC Builder | Generate Software Executables for Multicore Models