处理器在环仿真

处理器在环 (PIL) 仿真交叉编译生成的源代码,然后在目标硬件上下载并运行目标代码。通过比较普通模式仿真结果和 PIL 仿真结果,可以测试模型与生成的代码之间是否存在数值等效性。在 PIL 仿真期间,您可以为生成的代码收集代码覆盖率和执行时间度量。

PIL 仿真需要连接配置。

App

| SIL/PIL 管理器 | 验证生成的代码 |

命名空间

target | 管理目标硬件和构建工具信息 |

类

对象

函数

主题

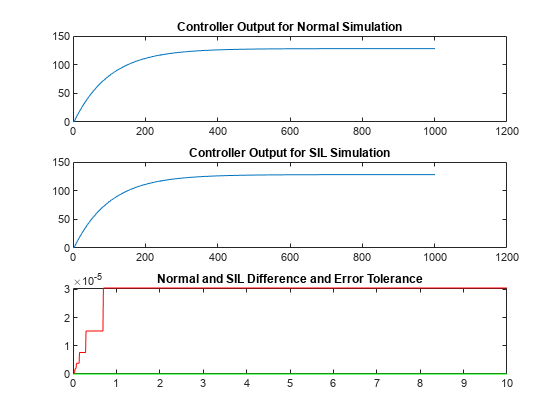

- SIL 和 PIL 仿真

软件在环 (SIL) 和处理器在环 (PIL) 仿真概述。

- 选择 SIL 或 PIL 方法

测试从顶层模型、引用模型或子系统生成的代码。

- 为 Simulink 创建 PIL 目标连接配置

为您的目标环境自定义 PIL 仿真。

- Host-Target Communication for Simulink PIL Simulation

Use the

rtiostreamAPI for communication between your development computer and target hardware during a PIL simulation. - Specify Hardware Timer for Simulink

Specify a hardware timer using the Code Replacement Tool.

- Set Up PIL Connectivity by Using Target Framework

Provide PIL connectivity between Simulink® and the target hardware.

- Custom Toolchain Directives Required for Code Coverage and Execution Profiling

Specify compiler directives for building PIL application that supports code coverage analysis and execution profiling.

- 配置并运行 PIL 仿真

设置和运行顶层模型 PIL、Model 模块 PIL 和 PIL 模块仿真。

- 使用 SIL/PIL 管理器的单元测试子系统代码

使用 SIL/PIL 管理器对原子子系统执行单元测试。

- SIL/PIL Manager Verification Workflow

A simplified workflow for verifying generated code.

- PIL Simulation Sequence

How a PIL simulation proceeds.

- Simulation Mode Override Behavior in Model Reference Hierarchy

How the simulation mode of the top model or parent model determines the simulation behavior of a model hierarchy.

- 永磁同步电机的磁场定向控制

仿真电机控制系统,生成控制器代码,并使用 PIL 仿真测试数值等效性和探查代码执行时间。

- PIL 仿真的安全性

PIL 仿真的安全措施。

- SIL and PIL Limitations

Modeling and code generation features that are not supported or partially supported by SIL and PIL simulations.

疑难解答

Debug Generated Code During SIL or PIL Simulation

Use a debugger to understand the behavior of generated code.

View SIL and PIL Files in Code Generation Report

Produce a code generation report and static code metrics that cover SIL and PIL files.

Verification of Code Generation Assumptions

The SIL or PIL simulation checks code generation assumptions.