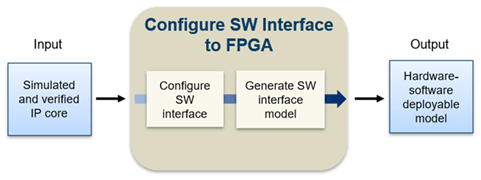

Configure Software Interface to FPGA

Create a software interface model that contains the algorithm to run on the embedded processor on your target platform. The input is your tested and verified IP core model. The output is the software interface model containing the communication between the FPGA and processor and the algorithm that deploys to the embedded processor on-board your SoC device or Simulink® Real-Time™ target machine. For more details on the workflow, see Targeting FPGA & SoC Hardware Overview.

Topics

- Choose a Method to Interact with IP Cores on Target Hardware

Choose a software interface method to interact with IP cores running on target hardware.

- Generate Software Interface Model to Probe and Rapidly Prototype HDL IP Core

Generate software interface model to communicate with the HDL IP core and perform rapid prototyping.

- Generate Device Tree for IP Core

Generate device tree files that include the HDL Coder™ generated IP core.