FPGA 浮点库

映射到 Altera® 和 Xilinx® FPGA 浮点库

您可以映射到浮点库来综合浮点设计,而无需从浮点设计转换为定点设计。消除此转换步骤可减少数据精度损失,并使您能够对更宽的动态范围进行建模。

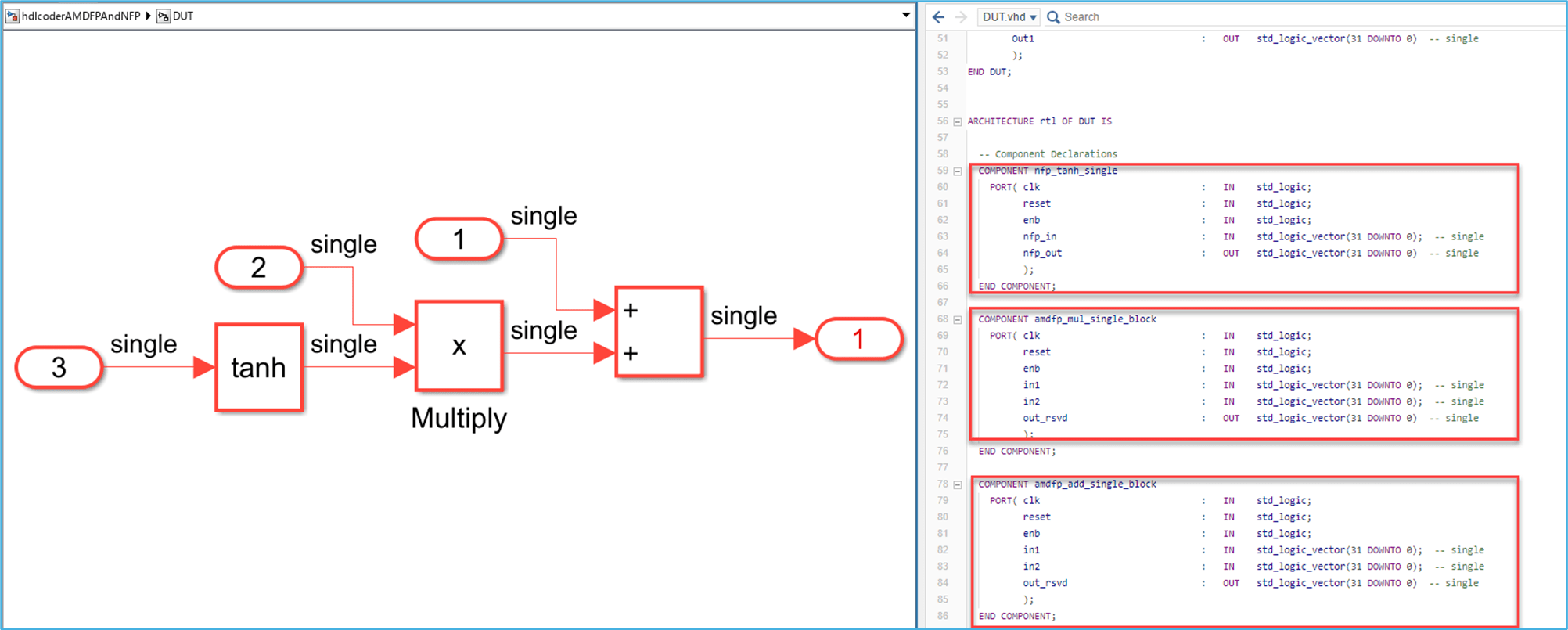

如果模型设计使用 Single 或 Double 数据类型,请使用 FPGA 浮点目标库为 Simulink® 模型生成代码。HDL Coder™ 可以将您的设计映射到原生浮点库和供应商特定的 FPGA 浮点库,例如 Altera 或 Xilinx FPGA 浮点库。同时使用原生浮点和供应商特定 IP 可以更高效地利用 FPGA 上的资源,例如硬化的 DSP 浮点加法器或乘法器基元,这样就可以在 FPGA 结构中实现更大的设计。这种混合设计对于大型复杂模型是有利的。

类

hdlcoder.FloatingPointTargetConfig | Floating-point target configuration for floating-point library |

hdlcoder.FloatingPointTargetConfig.IPConfig | IP settings for selected floating-point configuration |

主题

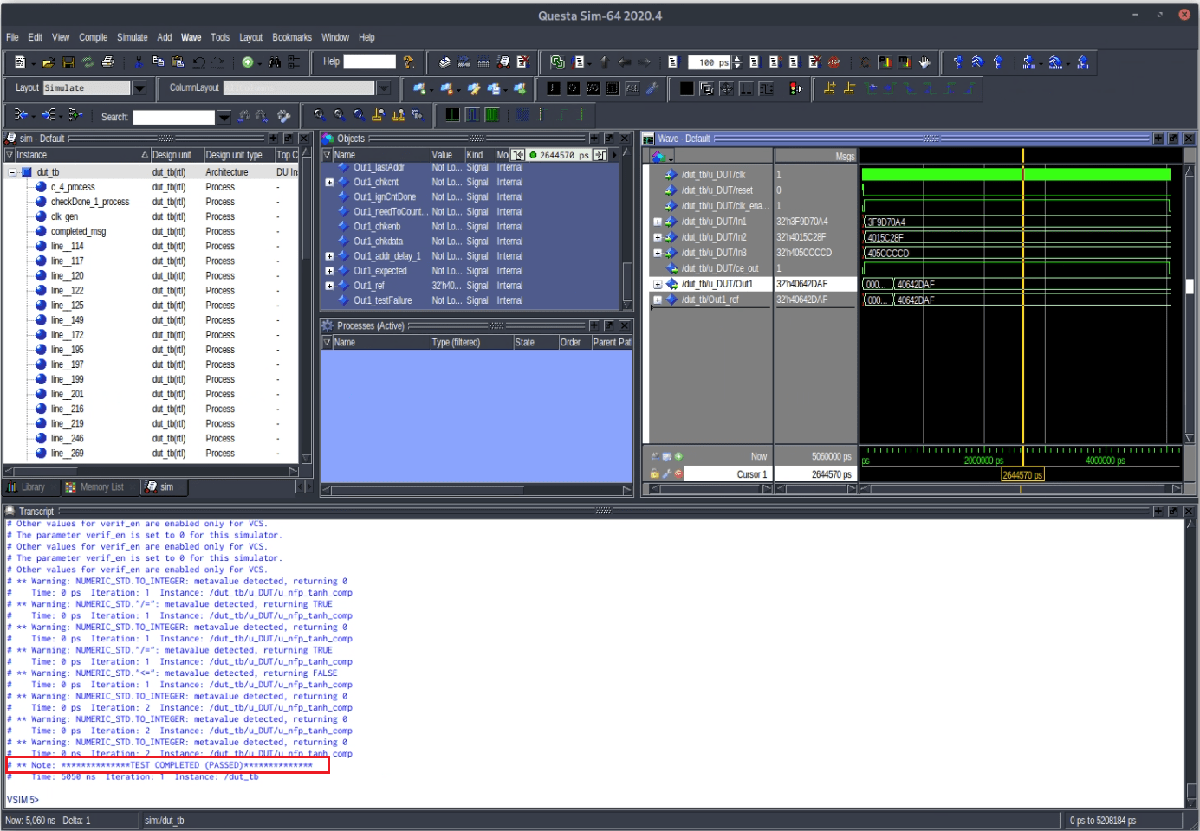

- Generate HDL Code for Vendor-Specific FPGA Floating-Point Target Libraries

How to set up and generate HDL code for Altera and AMD floating-point target libraries.

- Customize Floating-Point IP Configuration

Learn how to customize the latency or target frequency of the floating-point IP library.

- HDL Coder Support for FPGA Floating-Point Library Mapping

Blocks supported in Simulink for mapping to floating-point target libraries.