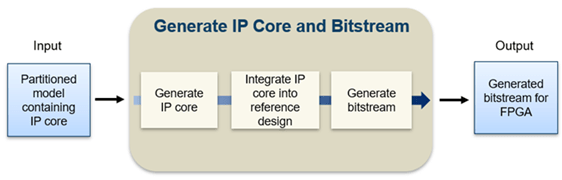

生成 IP 核和比特流

生成包含 HDL 代码的 HDL IP 核和比特流,用于部署在独立的 Intel® FPGA 板和 SoC 器件上

IP 核是实现特定函数(通常是算法)的可共享和可重用 HDL 组件。一个 IP 核包含 IP 核定义文件、为算法生成的 HDL 代码、包含寄存器地址映射的 C 头文件和 IP 核报告。

通过使用 HDL 工作流顾问中的 IP Core Generation 工作流,HDL Coder™ 可以生成 IP 核(其中包含 HDL 源代码和用于将 IP 核集成到 Vivado® 工程中的 C 头文件),然后对目标硬件进行编程。您可以根据目标平台将 IP 核集成到默认或自定义参考设计中,并生成要部署到 FPGA 硬件的比特流。输入是 Simulink® 模型或 MATLAB® 函数中设计的 IP 核。输出是由 HDL Coder 从 IP 核生成的比特流。

类别

- 自定义 IP 核生成

从 DUT 生成 HDL IP 核以部署到默认系统参考设计或注册到板的自定义参考设计

- 参考设计集成和部署

将生成的 IP 核集成到默认系统参考设计中

- 自定义板和参考设计

为 Intel SoC 器件定义和注册自定义参考设计或自定义板