速度优化

通过缩短关键路径来改进目标 FPGA 或 SoC 器件设计的时序和时钟速度。您可以使用不同流水线方法来缩短关键路径。有关速度优化的概述,请参阅Speed and Area Optimizations in HDL Coder。

函数

hdlcoder.optimizeDesign | Automatic iterative HDL design optimization |

hdlcoder.supportedDevices | Show supported target hardware and device details |

类

hdlcoder.OptimizationConfig | hdlcoder.optimizeDesign configuration object |

模块

主题

- Adaptive Pipelining

Automatic pipeline insertion based on the target device, target frequency, and multiplier word-lengths.

- Clock-Rate Pipelining

Pipeline registers insertion at the faster clock rate instead of the slower data rate.

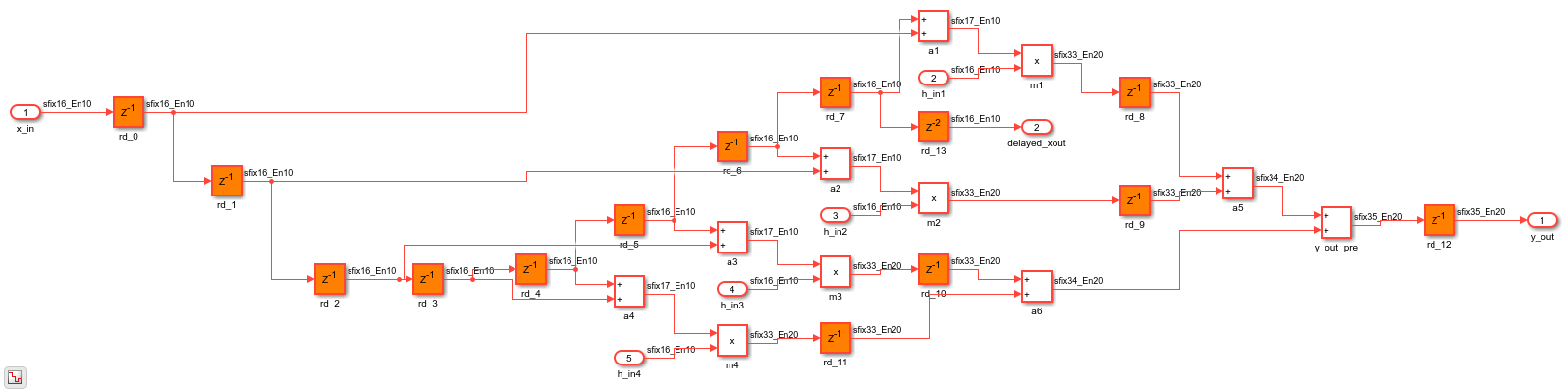

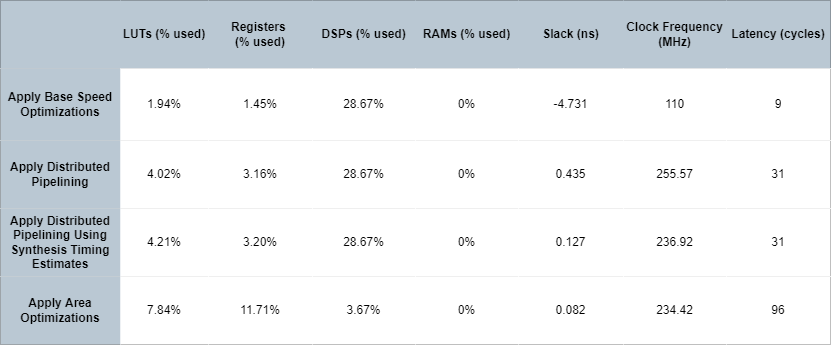

- Distributed Pipelining

Definition, benefits, and costs of distributed pipelining.

- Distributed Pipelining Using Synthesis Timing Estimates

Use synthesis timing estimates for distributed pipelining to more accurately reflect how components function on hardware to better distribute pipelines and increase clock frequency for your target device.

- Constrained Output Pipelining

Constrained output pipelining definition and use case.

- Automatic Iterative Optimization

How automatic iterative optimization works, prerequisites and restrictions.

- Critical Path Estimation Without Running Synthesis

Find the estimated critical paths in your design without using third-party synthesis tools.

- Generate Custom Timing Database for Custom Tools and Devices

Create a custom timing generator to characterize custom devices for your custom tools.

- Design Patterns That Require Adaptive Pipelining

For certain design patterns, you must enable the adaptive pipelining optimization to meet the timing requirements.

- Use Distributed Pipelining Optimization in Models with MATLAB Function Blocks

How to optimize HDL code for MATLAB Function blocks for speed by distributing design delays and generated pipeline stages.

- HDL Optimizations Across MATLAB Function Block Boundary Using MATLAB Datapath Architecture

Apply optimizations inside and across MATLAB Function blocks with other Simulink® blocks.

疑难解答

Resolve Simulation Mismatch When Pipelining with a Feedback Loop Outside the DUT

Learn how to resolve simulation mismatch issues when using pipeline optimizations with feedback loops.