Resolve Simulation Mismatch When Pipelining with a Feedback Loop Outside the DUT

This example shows how to use pipelining optimizations to resolve a simulation mismatch between the generated model and original model after HDL code generation.

Issue

If you have a feedback loop around your device under test (DUT) subsystem and pipeline optimizations enabled in the DUT, you might have a simulation mismatch between your generated and original model. This mismatch is due to added latency from delays or pipeline registers in the DUT of the generated model that are not present in the original model DUT. A simulation mismatch shows that your original and generated model, and your original model and generated HDL code, are not functionally equivalent.

HDL Coder™ generates code only for your DUT and nothing outside of that in your model. As a result, the simulation mismatch does not cause code generation errors. The mismatch is also not seen in the validation model because it is comparing only the original model DUT to the generated model DUT.

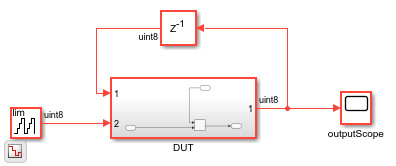

This issue can be seen in the feedback_loop_outsideDUT model. In the model, the feedback delay is outside of the DUT subsystem that HDL Coder generates code for.

open_system("feedback_loop_outsideDUT");

This is the outputScope of the original model.

sim("feedback_loop_outsideDUT"); open_system("feedback_loop_outsideDUT/outputScope");

In the model, the HDL Block properties InputPipeline and OutputPipeline are set to 1 for the Add block. These properties place a delay block, which acts as a pipeline register, before and after the Add block to add pipelines in the combinatorial path and increase the clock frequency of your design. Because there are options enabled to add pipelines in the generated model and HDL code, delay balancing is enabled (its default) for the model. It is recommended to keep delay balancing enabled to balance delays added in your design. For more information, see Understand Delay Balancing in HDL Coder.

hdlsaveparams("feedback_loop_outsideDUT");%% Set Model 'feedback_loop_outsideDUT' HDL parameters

hdlset_param('feedback_loop_outsideDUT', 'GenerateHDLCode', 'off');

hdlset_param('feedback_loop_outsideDUT', 'GenerateValidationModel', 'on');

hdlset_param('feedback_loop_outsideDUT', 'HDLSubsystem', 'feedback_loop_outsideDUT/DUT');

% Set SubSystem HDL parameters

hdlset_param('feedback_loop_outsideDUT/DUT', 'ClockRatePipelining', 'off');

% Set Sum HDL parameters

hdlset_param('feedback_loop_outsideDUT/DUT/Add', 'InputPipeline', 1);

hdlset_param('feedback_loop_outsideDUT/DUT/Add', 'OutputPipeline', 1);

Generate HDL code. In the MATLAB Command Window, a message during code generation shows that two cycles of latency have been introduced in the generated model. The latency is not compensated for during code generation because the feedback loop is outside of the DUT. Because of the latency introduced, the original model and generated model have a simulation mismatch.

makehdl("feedback_loop_outsideDUT/DUT");### Working on the model feedback_loop_outsideDUT ### Generating HDL for feedback_loop_outsideDUT/DUT ### Using the config set for model feedback_loop_outsideDUT for HDL code generation parameters. ### Running HDL checks on the model 'feedback_loop_outsideDUT'. ### Begin compilation of the model 'feedback_loop_outsideDUT'... ### Working on the model 'feedback_loop_outsideDUT'... ### The code generation and optimization options you have chosen have introduced additional pipeline delays. ### The delay balancing feature has automatically inserted matching delays for compensation. ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 2 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_feedback_loop_outsideDUT'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/feedback_loop_outsideDUT/gm_feedback_loop_outsideDUT.slx ### Generating new validation model: 'gm_feedback_loop_outsideDUT_vnl'. ### Validation model generation complete. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'feedback_loop_outsideDUT' complete with 0 errors, 0 warnings, and 1 messages.

Open and run the generated model.

open_system("gm_feedback_loop_outsideDUT");

In the outputScope of the generated model, compare the scopes of the original and generated model to see the simulation mismatch between the two scopes.

sim("gm_feedback_loop_outsideDUT"); open_system("gm_feedback_loop_outsideDUT/outputScope");

Potential Solutions

Use Clock-Rate Pipelining

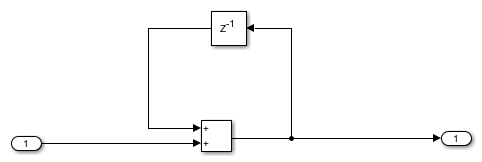

To fix this issue, it is recommended to bring the design delay inside of the DUT subsystem so it can be taken into account during HDL code generation. The feedback delay is brought into the DUT in the model feedback_loop_inDUT. HDL Coder then takes the entire feedback loop into account during code generation.

modelname = "feedback_loop_inDUT"; load_system(modelname); dutname = "feedback_loop_inDUT/DUT"; open_system(dutname);

When you generate code for this DUT by using the makehdl command, this delay balancing error is displayed in the MATLAB Command Window:

Delay balancing unsuccessful because Delay introduced in feedback loop cannot be path balanced. Offending Block:feedback_loop_inDUT/DUT/Add_out_pipe.

While the error in the HDL code generation is about unsuccessful delay balancing, the delay balancing issue is a result of pipelining in feedback loops that introduce latency and break functional equivalence between the original and generated model. To pipeline your design inside a feedback loop by using optimization options, such as the HDL Block properties InputPipeline and OutputPipeline for blocks in your DUT, use a faster clock rate and enable the clock-rate pipelining optimization. For more information, see Clock-Rate Pipelining.

In the feedback_loop_inDUT model, to use clock-rate pipelining:

Set an oversampling factor of 10 to increase the clock rate to be 10x the model base rate, or data rate.

Enable clock-rate pipelining for the DUT.

hdlset_param(modelname, "Oversampling", 10) hdlset_param(dutname, "ClockRatePipelining", "on");

Now, when you generate code, there are no errors and the latency decreases from two data rate cycles to one cycle. The latency that remains is a result of the feedback loop in the DUT. The latency is not added during code generation.

makehdl(dutname);

### Working on the model feedback_loop_inDUT ### Generating HDL for feedback_loop_inDUT/DUT ### Using the config set for model feedback_loop_inDUT for HDL code generation parameters. ### Running HDL checks on the model 'feedback_loop_inDUT'. ### Begin compilation of the model 'feedback_loop_inDUT'... ### Working on the model 'feedback_loop_inDUT'... ### The code generation and optimization options you have chosen have introduced additional pipeline delays. ### The delay balancing feature has automatically inserted matching delays for compensation. ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 1 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_feedback_loop_inDUT'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/feedback_loop_inDUT/gm_feedback_loop_inDUT.slx ### Generating new validation model: 'gm_feedback_loop_inDUT_vnl'. ### Validation model generation complete. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'feedback_loop_inDUT' complete with 0 errors, 0 warnings, and 2 messages.

Open and run the generated model.

open_system("gm_feedback_loop_inDUT");

sim("gm_feedback_loop_inDUT");You can now compare the original model feedback_loop_inDUT to the generated model gm_feedback_loop_inDUT by using the output scopes of the original and generated models. The simulation of the original model with the feedback loop inside or outside the DUT is the same simulation. The generated model with the feedback loop inside the DUT now has a functionally matching output scope, delayed by one data rate cycle of latency.

open_system("gm_feedback_loop_inDUT/Scope1");

The output scope shows that the original and generated model are now functionally equivalent. This functional equivalence can also be seen by using the validation model because the feedback loop is inside the DUT and you can directly compare the two DUTs.

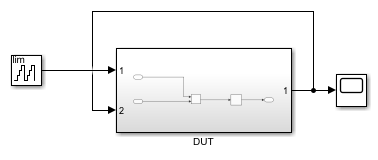

Now that the issue is fixed by using clock-rate pipelining, for design purposes, you can move the feedback loop wire outside of the DUT while keeping the delay inside the DUT. This option enables you to maintain your original design as much as possible, while fixing the simulation mismatch with clock-rate pipelining.

modelname = "delay_inDUT"; load_system(modelname); dutname = "delay_inDUT/DUT"; open_system(modelname);

Applying this solution means that the delay balancing error during code generation is not generated. As a result, the simulation issue is not indicated during code generation when you move only the delay inside the DUT and have disabled clock-rate pipelining.

makehdl(dutname);

### Working on the model delay_inDUT ### Generating HDL for delay_inDUT/DUT ### Using the config set for model delay_inDUT for HDL code generation parameters. ### Running HDL checks on the model 'delay_inDUT'. ### Begin compilation of the model 'delay_inDUT'... ### Working on the model 'delay_inDUT'... ### The code generation and optimization options you have chosen have introduced additional pipeline delays. ### The delay balancing feature has automatically inserted matching delays for compensation. ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 1 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_delay_inDUT'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/delay_inDUT/gm_delay_inDUT.slx ### Generating new validation model: 'gm_delay_inDUT_vnl'. ### Validation model generation complete. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'delay_inDUT' complete with 0 errors, 0 warnings, and 1 messages.

Even though there is no delay balancing error to fix during code generation, the simulation mismatch still needs to be fixed. This requires the same solution of setting the oversampling factor and enabling clock-rate pipelining. Removing the feedback loop from the DUT but keeping the design delay inside allows the design delay to be absorbed and reduces the latency to zero.

hdlset_param(modelname, "Oversampling", 10) hdlset_param(dutname, "ClockRatePipelining", "on"); makehdl(dutname);

### Working on the model delay_inDUT ### Generating HDL for delay_inDUT/DUT ### Using the config set for model delay_inDUT for HDL code generation parameters. ### Running HDL checks on the model 'delay_inDUT'. ### Begin compilation of the model 'delay_inDUT'... ### Working on the model 'delay_inDUT'... ### Working on... GenerateModel ### Begin model generation 'gm_delay_inDUT'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/delay_inDUT/gm_delay_inDUT.slx ### Generating new validation model: 'gm_delay_inDUT_vnl'. ### Validation model generation complete. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'delay_inDUT' complete with 0 errors, 0 warnings, and 1 messages.

Open and run the generated model. You can compare the output scopes of the original and generated model after code generation to see the issue is resolved and there is no added latency during code generation.

open_system("gm_delay_inDUT");

This is the output scope of the original model delay_inDUT.

sim("delay_inDUT"); open_system("delay_inDUT/Scope1");

This is the output scope of the generated model gm_delay_inDUT.

sim("gm_delay_inDUT"); open_system("gm_delay_inDUT/Scope1");

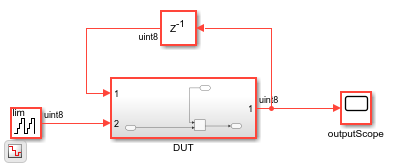

Disable Optimizations That Add Latency

To keep the feedback loop outside of the DUT with no added latency to the generated model, remove all optimizations that add pipelines to your generated model and HDL code. In this example, remove the input and output pipelines optimization options that are specified for the Add block in your DUT subsystem in the feedback_loop_outsideDUT model.

modelname = "feedback_loop_outsideDUT"; dutname = "feedback_loop_outsideDUT/DUT"; open_system(modelname); hdlset_param("feedback_loop_outsideDUT/DUT/Add", "InputPipeline", 0); hdlset_param("feedback_loop_outsideDUT/DUT/Add", "OutputPipeline", 0);

Removing the input and output pipelines removes the added latency to the generated model. The original and generated model are now functionally equivalent with no simulation mismatch. To compare the original and generated model scope outputs, generate HDL code.

makehdl(dutname)

### Working on the model feedback_loop_outsideDUT ### Generating HDL for feedback_loop_outsideDUT/DUT ### Using the config set for model feedback_loop_outsideDUT for HDL code generation parameters. ### Running HDL checks on the model 'feedback_loop_outsideDUT'. ### Begin compilation of the model 'feedback_loop_outsideDUT'... ### Working on the model 'feedback_loop_outsideDUT'... ### Working on... GenerateModel ### Begin model generation 'gm_feedback_loop_outsideDUT'... ### Copying DUT to the generated model.... ### Model generation complete. ### Generated model saved at hdlsrc/feedback_loop_outsideDUT/gm_feedback_loop_outsideDUT.slx ### Generating new validation model: 'gm_feedback_loop_outsideDUT_vnl'. ### Validation model generation complete. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'feedback_loop_outsideDUT' complete with 0 errors, 0 warnings, and 1 messages.

Open and run the generated model.

open_system("gm_feedback_loop_outsideDUT");

This is the output scope of the original model feedback_loop_outsideDUT.

sim("feedback_loop_outsideDUT"); open_system("feedback_loop_outsideDUT/outputScope");

This is the output scope of the generated model gm_feedback_loop_outsideDUT.

sim("gm_feedback_loop_outsideDUT"); open_system("gm_feedback_loop_outsideDUT/outputScope");

Redesign the Model to Handle Added Latency

If you prefer to keep the pipeline optimization in your design, you can redesign your model to handle the added latency in order to remove the simulation mismatch. For example, you can redesign your model to no longer contain a feedback loop. If you remove the feedback loop, HDL Coder can balance delays to handle the added latency and maintain functional equivalence between the original and generated model to avoid a simulation mismatch.

See Also

Guidelines for Using Delays and Goto and From Blocks for HDL Code Generation