Understand Delay Balancing in HDL Coder

To achieve more efficient hardware usage and higher clock-rates in your model, HDL Coder™ has several optimizations, block implementations, and options that add discrete latency into your generated model in the form of introduced Delay blocks. Optimizations such as output pipelining, streaming, or resource sharing can introduce such latency. Some block implementations, such as the Newton-Raphson and CORDIC architecture, inherently introduce latency in signal paths in the generated HDL code. When optimizations or block implementation options introduce latency along the critical path in a model, the numerical calculations of the original model and the generated model or HDL code can differ from each other in certain time steps because equivalent delays are not introduced on other, parallel signal paths.

If cycle-accurate equivalence between the original model and the generated model or HDL code is a design requirement, you can manually add Delay blocks to your model to compensate for introduced latency. To make feedback loop behavior cycle-accurate, you can also add compensating Delay blocks. For an example, see Use Delay Absorption While Modeling with Latency. However, manual addition of compensating Delay blocks is prone to error and does not scale well to large models that have many signal paths or multiple sample rates.

The delay balancing optimization matches the numerical calculations at each time step between the original model and the generated model or HDL code. With delay balancing, HDL Coder detects introduced latency along one path and then inserts matching delays on the other paths in your generated model.

Control Scope of Delay Balancing

Delay balancing is enabled by default when you generate code with HDL Coder. You can disable delay balancing for specific parts of your design by using the HDL block property BalanceDelays for input and output ports. See Delay Balancing Considerations and Enabling Optimizations in HDL Coder.

Disable Delay Balancing for Constant Sources

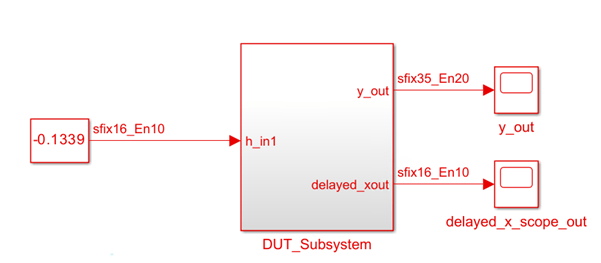

A stable path is a path where the initial source to the

path is constant. If your model contains a stable path outside the DUT and

connects to the top-level DUT subsystem and you want to reduce the amount of

resources needed, you can disable delay balancing

for the stable path by disabling the HDL block property

BalanceDelays on the DUT-level Inport

block. The BalanceDelays property affects only DUT-level

Inport blocks. For example, in this model, you can disable

BalanceDelays for the

DUT_Subsystem's Inport block, which is also

input port h_in1, because the input to the

Inport block is a Constant block.

To disable the HDL block property BalanceDelays for an Inport block from the HDL Block Properties dialog box:

Right-click the Inport block.

In the HDL Coder app section, select HDL Block Properties.

Set BalanceDelays to

off.

To disable delay balancing for an Inport block

from the command line, use the hdlset_param function.

If your DUT includes a subsystem hierarchy and you disable BalanceDelays on the DUT-level Inport block, the delay balancing on the stable path does not occur within the lower-level hierarchy if the stable path extends to that lower-level hierarchy. For an example, see Control the Scope of Delay Balancing.

Note

If distributed pipelining is enabled for the model and you disable

BalanceDelays on DUT-level Inport

blocks for stable paths, delays may be inserted on stable paths in the

generated model. To avoid the insertion of delays on stable paths in the

generated model, change the Pipeline distribution

priority configuration parameter from Numerical

Integrity to Performance. For

more information, see Pipeline distribution priority.

To disable the HDL block property BalanceDelays for an Outport block using the HDL Block Properties dialog box:

Right-click the Outport block.

In the HDL Coder app section, select HDL Block Properties.

Set BalanceDelays to

off.

To disable delay balancing for an Outport block

from the command line, use the hdlset_param function.

If your model contains a stable path that originates in the DUT, meaning that there is a Constant block as an input in the DUT, and a parallel path to the stable path has latency introduced from optimizations, delay balancing does not insert a matching delay on the stable path that contains the Constant block, because the output value of the block is a constant. Not inserting the delay results in less resources needed for the design, but also results in a simulation mismatch during initialization cycles. To resolve the simulation mismatch, you can manually add matching delays to the Constant block path by setting the HDL block property OutputPipeline to the number of matching delays needed at the output of the Constant block.

Delay Balancing Report

When you generate code for a DUT, HDL Coder produces an optimization report. The DUT can be a subsystem, model, or model reference.

The Delay Balancing report shows latency changes, pipeline and phase delay at the output ports, and delay absorption information. If delay balancing fails, the report displays the criteria that was violated and a link to blocks or subsystems that cause delay balancing to fail.

Delay Balancing Considerations

When you generate HDL code with optimizations enabled, you must balance pipelines introduced during these optimizations. Failure to balance automatically inserted pipeline delays can cause numerical calculation mismatches in generated code deployed in hardware.

For multirate models, HDL Coder may insert a large number of pipeline registers in the generated code, potentially consuming a large amount of resources on your hardware. For instructions on how to minimize this resource usage, see Optimize Latency and Area for Multirate Designs and Optimize Generated HDL Code for Multirate Designs with Large Rate Differentials.

Resolve Delay Balancing Errors in a Feedback Loop Design

When you generate HDL code for a model that contains a feedback loop in the DUT subsystem, the Clock-Rate Pipelining report and Delay Balancing report list the extra cycles of latency introduced by optimizations in the feedback loop that cannot be offset using design delays for the loop latency budget. Disabling delay balancing for the entire model results in a simulation mismatch between your original model and the generated model. To resolve this mismatch, either:

Use clock-rate pipelining. See Use Clock-Rate Pipelining in Resolve Simulation Mismatch When Pipelining with a Feedback Loop Outside the DUT.

Increase the latency budget by adding more design delays. See Model with Latency in a Feedback Loop in Use Delay Absorption While Modeling with Latency.

Resolve Delay Balancing Errors in a Conditional Subsystem

When you generate HDL code for a model with a conditional subsystem within the DUT subsystem, the Clock-Rate Pipelining report and Delay Balancing report detail any extra cycles of latency introduced by optimizations in the conditional subsystem that cannot be offset while maintaining functional equivalence with the design model.

To balance the latency, add equivalent latency inside of the conditional subsystem by using a Delay block. For an example, see the Edit the Model section of the Resolve Delays Not Absorbed During Delay Balancing troubleshooting topic.

Delay Balancing Limitations

Subsystem-Level Restrictions

HDL Coder does not support delay balancing if a subsystem with

BlackBox architecture has the

ImplementationLatency block property set to a negative

value.

To fix this error, for ImplementationLatency, enter a non-negative integer.

Sample Time Restrictions

HDL Coder does not support delay balancing if you introduce latency from optimizations and:

The sample time is continuous.

Your design has an infinite sample time output.

See Also

Topics

- Create and Use Code Generation Reports

- Generated Model and Validation Model

- Check for blocks that have nonzero output latency

- Delay Balancing and Validation Model Workflow in HDL Coder

- Use Delay Absorption While Modeling with Latency

- Control the Scope of Delay Balancing

- Optimize Latency and Area for Multirate Designs