Zynq RFSoC Template Builder

Generate template model based on selected RFSoC reference design

Since R2021a

Add-On Required: This feature requires the HDL Coder Support Package for AMD FPGA and SoC Devices add-on.

Description

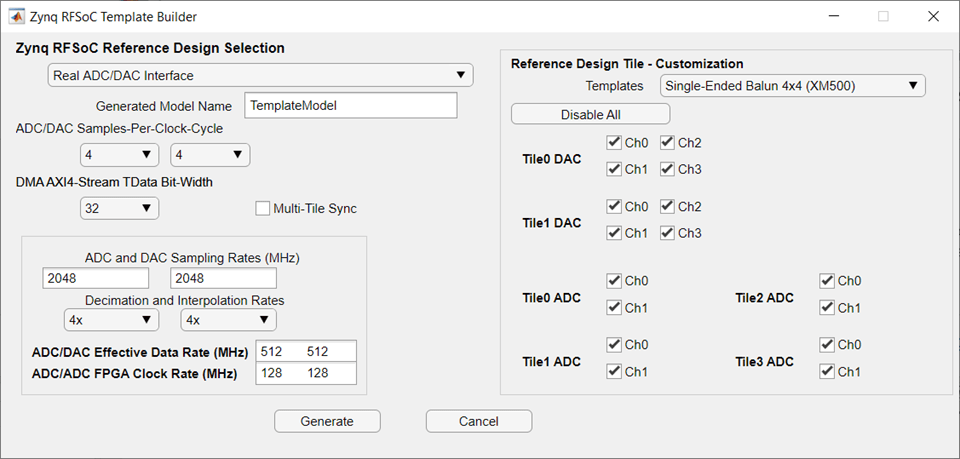

The Zynq RFSoC Template Builder tool enables you to select an RFSoC reference design and configure it to create a DUT template model.

Choose the reference design, set the analog-to-digital converter (ADC) and digital-to-analog converter (DAC) sample rates and data bit-width, and customize the design with preconfigured channels. The Zynq RFSoC Template Builder tool creates a simple DUT model and connects the model to the interface of the reference design. Use the Zynq RFSoC Template Builder to perform the following actions:

Create an HDL model with the required I/O blocks connected.

Configure the model with the selected board and reference design. This action automates step 1.1 and 1.2 in the HDL Workflow Advisor app.

Set the target interface for the model input and output. This action automates step 1.3 in the HDL Workflow Advisor app.

Edit the generated DUT to include the required algorithm. Then, either simulate the system or generate and load a bitstream to an FPGA using HDL Workflow Advisor.

Open the Zynq RFSoC Template Builder

MATLAB® command prompt: Enter

rfsocTemplateBuilder('boardname').rfsocTemplateBuilder('zcu111')— Generate an RFSoC model for a ZCU111 board.rfsocTemplateBuilder('zcu216')— Generate an RFSoC model for a ZCU216 board.

Limitations

Use this tool only when targeting an RFSoC device using IP core generation workflow.

Do not use this tool when targeting an RFSoC device with other workflows.

Do not use this tool when targeting devices other than RFSoC.

Version History

Introduced in R2021a