Parallel Link Design

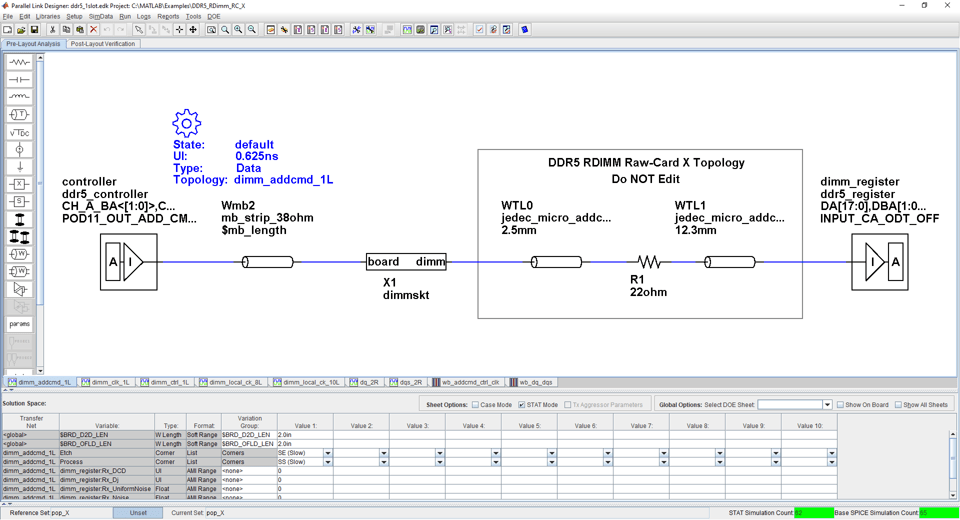

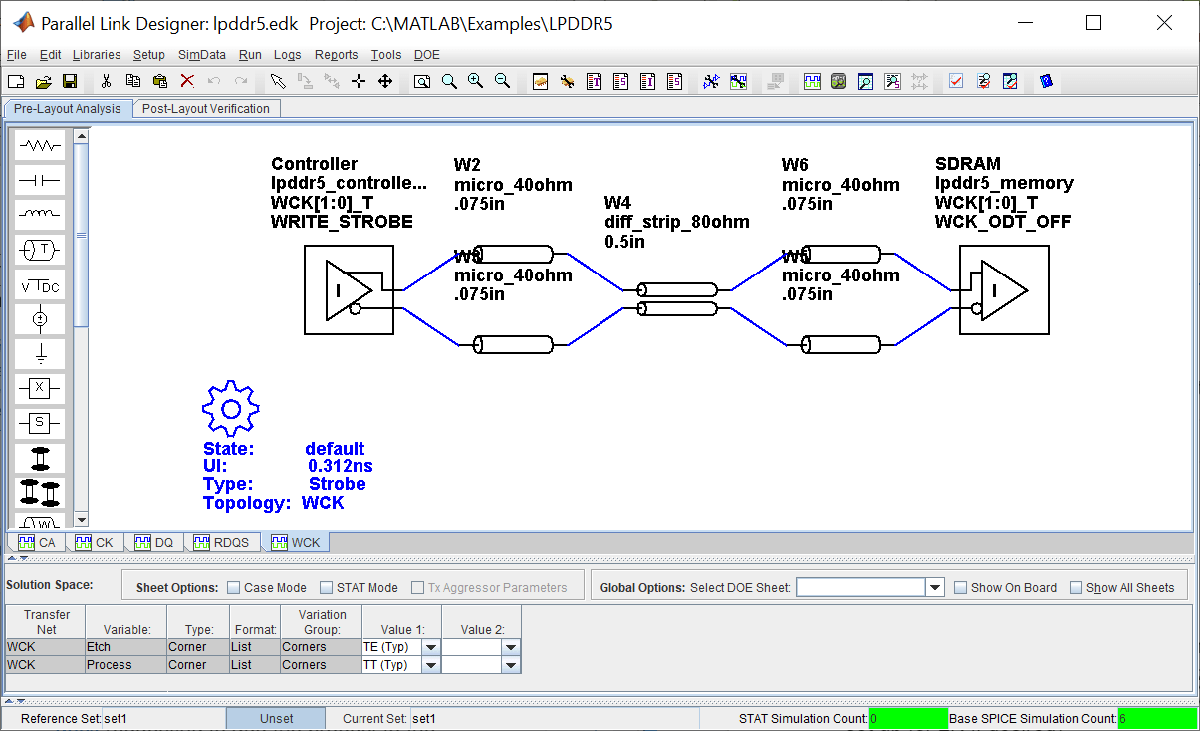

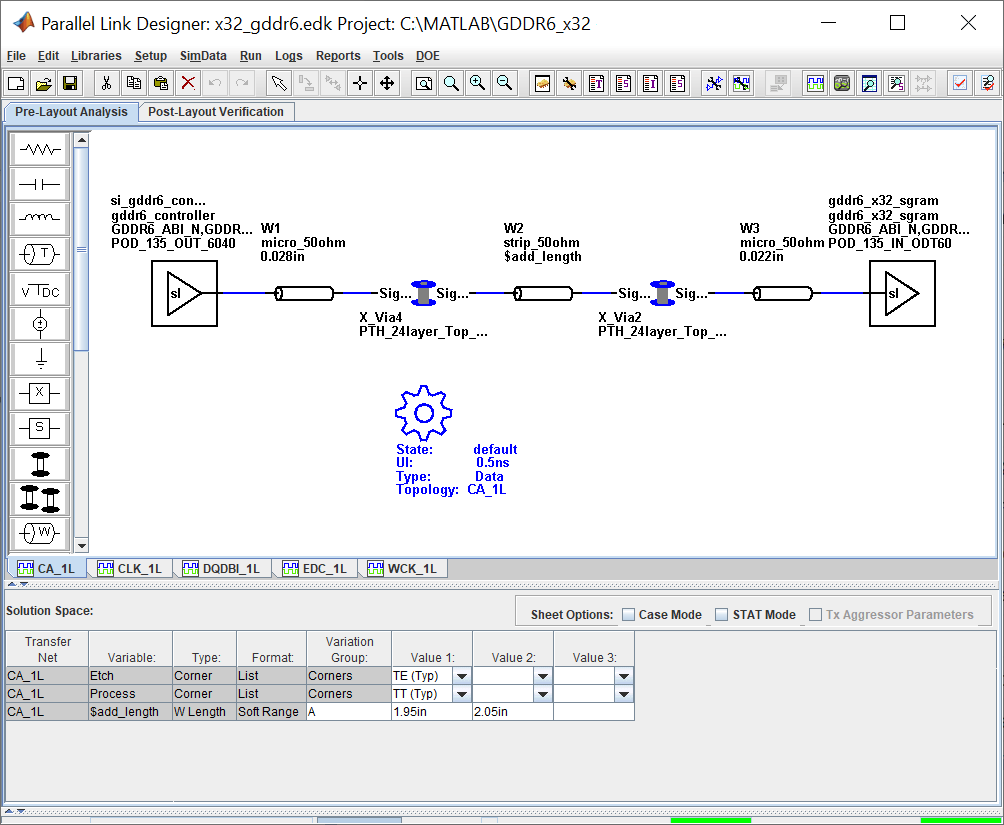

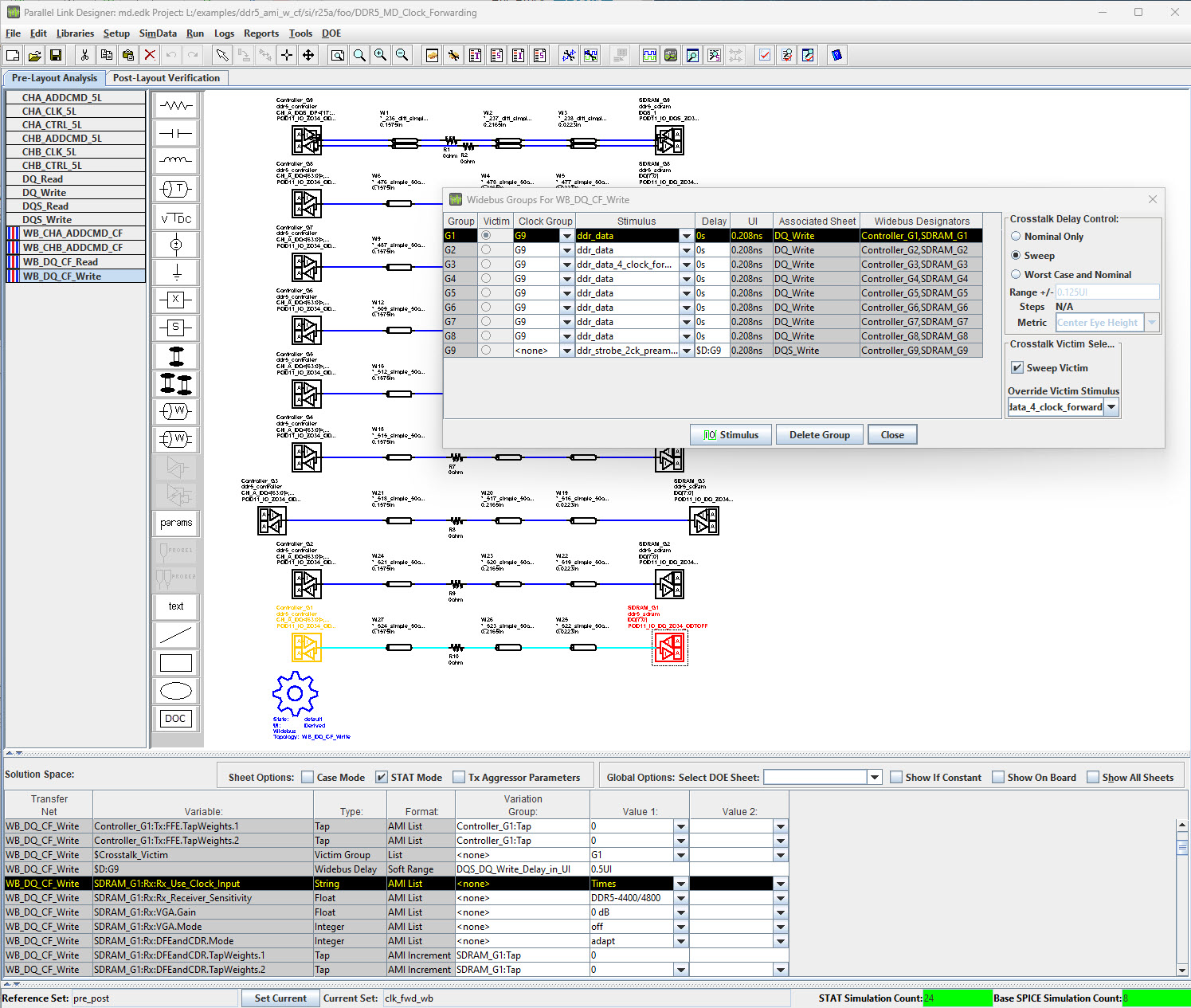

The Parallel Link Designer app provides a dedicated system-level design and analysis environment for parallel links. Capture your parallel link designs graphically and experiment with different physical layouts and parameter sweeping to determine setup/hold timing and voltage margins for high-speed parallel links. Analyze parallel interfaces for compliance with timing and signal integrity constraints.

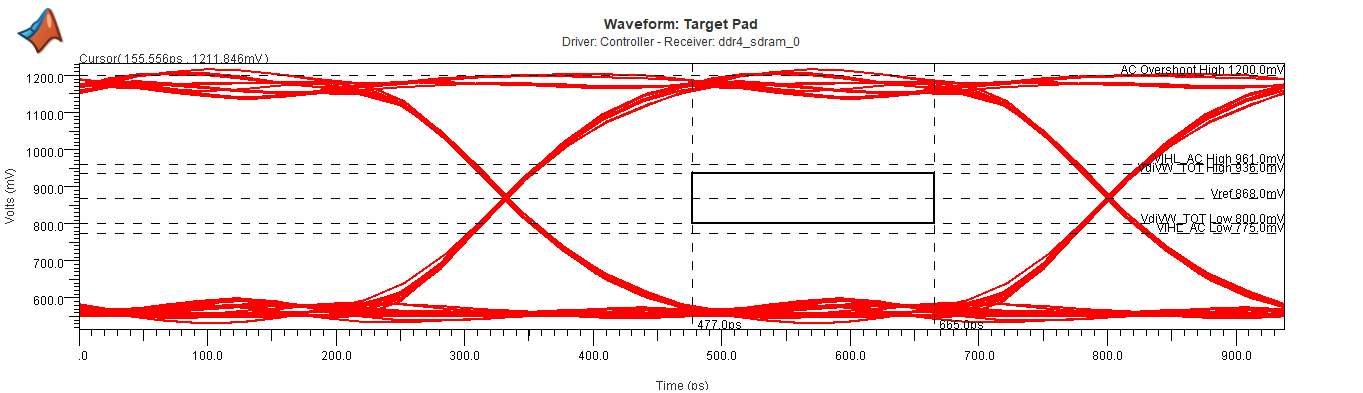

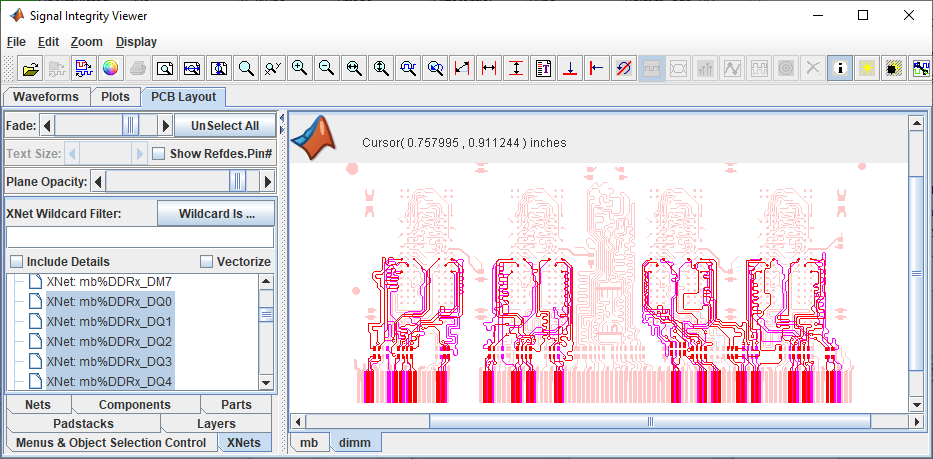

Use the Parallel Link Designer app to configure parallel links. Set simulation parameters, specify corner conditions, and define stimulus patterns. Set up pre-layout analysis to run SPICE and to conduct waveform and timing data analysis to analyze your custom parallel links. View and interpret the results using the Signal Integrity Viewer app. You can also set up and analyze the post-layout PCB database of your parallel link design if you have a license for RF PCB Toolbox™. You can modify the stackup and padstack models and customize vias and see how the changes impact your design.

Categories

- Parallel Link Design Concepts

Learn the basics of parallel link design projects using the Parallel Link Designer app

- Configure Parallel Link Projects

Configure parallel link projects for simulations

- Pre-Layout Analysis of Parallel Link Projects

Analyze parallel link projects before designing board layouts

- Post-Layout Verification of Parallel Link Projects

Verify the layout design of your system against design guidelines or specification rules

- Scripting in Parallel Link Projects

Use MATLAB scripting commands to control the Parallel Link Designer app

- Visualize and Interpret Parallel Link Project Analysis Results

Visualize and interpret the network characterization and statistical and time domain analysis results