Simulink Design Verifier 快速入门

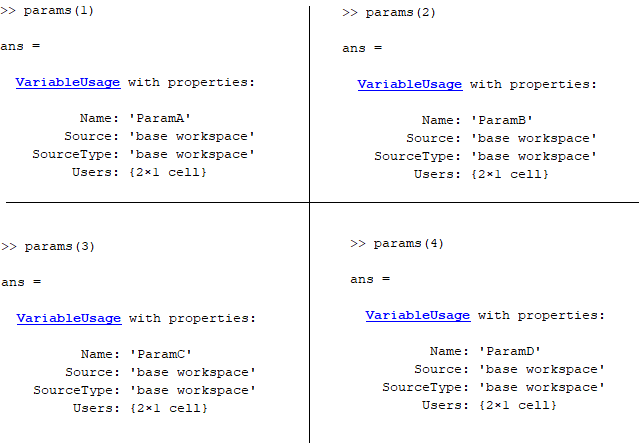

Simulink® Design Verifier™ 使用形式化方法来识别模型中隐藏的设计错误。它可以检测模型中导致整数溢出、死逻辑、数组访问违规和除以零的模块。它可以通过形式化方式验证设计是否满足功能需求。对于每个设计错误或需求违规,它都会生成一个用于调试的仿真测试用例。

Simulink Design Verifier 可为模型覆盖率和自定义目标生成测试用例,以扩展基于需求的现有测试用例。这些测试用例可驱动您的模型满足条件、决策、修正条件/决策 (MCDC) 和自定义覆盖率目标。除覆盖率目标之外,您还可以指定自定义测试目标以自动生成基于需求的测试用例。

对行业标准的支持可通过 IEC Certification Kit (for IEC 61508 and ISO 26262) 和 DO Qualification Kit (for DO-178) 获得。

教程

- 使用 Simulink Design Verifier 进行系统模型验证

了解 Simulink Design Verifier 分析的基础知识。

- 步骤 1: 准备模型以进行测试生成分析

- 步骤 2: 配置模型设置并运行分析

- 步骤 3: 查看测试生成分析结果

- 步骤 1: 准备模型以进行设计错误检测分析

- 步骤 2: 检测常见的设计错误

- 步骤 3: 执行设计错误检测分析

- 步骤 4: 查看设计错误检测分析结果

- 步骤 5: 修复模型中的设计错误

准备模型,配置模型设置,并查看测试生成分析结果。

配置模型设置、检测设计错误和查看结果。

精选示例

视频

什么是 Simulink Design Verifier?

Simulink Design Verifier 简介。

如何使用 Simulink Design Verifier 自动检测 Simulink 模型中的设计错误

使用 Simulink Design Verifier 查找设计中的错误,以及在检测到错误时如何使用 Simulink Design Verifier 中的可视化功能进行调试。

用于自动生成测试向量的 DO-178C 工作流

使用 Simulink Design Verifier 自动生成测试向量来分析 Simulink Coverage 收集的缺失模型覆盖率,以符合 DO-178C 及其补充规定。

如何调试属性证明反例

使用 Simulink Design Verifier™ 进行属性证明是一种静态分析方法,它使用形式化方法来证明给定属性是否始终有效。该方法可以帮助您通过形式化方式验证设计中实现的特定需求是否始终得到满足。

基于需求的测试工作流程

说明如何使用测试序列创建测试、定义形式化评估、将测试用例链接到需求、运行测试套件以及分析缺失的模型测试覆盖率。