HDL OFDM Receiver

This example shows how to implement an OFDM-based wireless receiver by using Simulink® blocks optimized for HDL code generation and hardware implementation.

The main purpose of this example is to model a custom HDL OFDM wireless communication receiver that can recover information in a real-time scenario. The model shown in this example receives data and decodes it based on the orthogonal frequency division multiplexing (OFDM). This model enables you to configure parameters: symbol modulation types such as BPSK, QPSK, 16-QAM, and 64-QAM and code rates 1/2, 2/3, 3/4 and 5/6 through punctured convolution encoding. This model enables you to control impairments such as carrier frequency offset (CFO), carrier phase offset (CPO), and rayleigh fading channel, which significantly affect an OFDM-based communication system. The model supports data rates up to 3 Mbps.

The receiver in this example works in conjunction with the transmitter in the HDL OFDM Transmitter example. The receiver in this example has a MATLAB® floating point equivalent function described in the HDL OFDM MATLAB References example.

Model Architecture

The following figure shows the architecture of an OFDM Receiver. The receiver samples the input at 30.72 Msps. These samples stream into the Decimation Filters. The output of the cascaded Decimation Filters streams into the Frequency Estimator and the Frequency Corrector. The Frequency Estimator and the Frequency Corrector estimate and correct CFO respectively and the samples stream into the Synchronizing Sequence (SS) Detector. The output of the SS Detector is used for the time synchronization. The time synchronized samples stream into the OFDM Demodulator, which demodulates the samples and generates frequency-domain subcarriers. The Subcarrier Parser parses the channel reference subcarriers, header subcarriers, and data subcarriers. The channel reference subcarriers stream into the Channel Estimator, which estimates the channel frequency response. The Channel Equalizer uses these estimates to equalize the header and data subcarriers in the frequency domain. The Header Recovery recovers the header information using the channel-equalized header subcarriers. The CPE Estimator estimates the common phase error (CPE) in the data sub carriers that get corrected by CPE Corrector. The Data Recovery uses the header information and the CPE-corrected data subcarriers to decode the data bits.

File Structure

These files are used to construct this example.

whdlOFDMReceiver— Top level OFDM receiver Simulink model.whdlOFDMRx— Reference model used by thewhdlOFDMReceivermodel.whdlexamples.OFDMRxSimulink— Initializes and runs thewhdlOFDMReceivermodel.whdlexamples.OFDMRxParameters— Initialization function forwhdlOFDMRx, initialized in the mask of the top subsystem of thewhdlOFDMRxmodel.whdlexamples.OFDMTx— MATLAB floating-point equivalent transmitter function that generates a transmitter waveform in thewhdlexamples.OFDMRxSimulinkfunction.whdlexamples.OFDMRx— MATLAB floating-point equivalent receiver function.

Receiver Interface

This figure shows the top-level model in this example.

Model Inputs:

dataIn — Input data, specified as a complex signed 16-bit signal sampled at 30.72 Msps.

validIn — Control signal to validate the dataIn, specified as a Boolean scalar.

reset — Control signal to reset the receiver while working on hardware.

impairmentControl — Bus signal to control the channel impairments.

The impairmentControl bus comprises the following signals:

frequencyOffsetCorrectionType — Control signal to indicate whether to select

Use internally estimated frequency offsetorUse externally provided frequency offsetoption for offset correction, specified as a Boolean scalar.externalFrequencyOffset — Real signed 14-bit CFO with range from -7400 Hz to 7400 Hz provided externally for CFO correction.

channelEqualizerControl — Control signal to indicate whether to enable or disable channel equalization, specified as a Boolean scalar.

CPECorrectionControl — Control signal to indicate whether to enable or disable CPE correction, specified as a Boolean scalar.

Model Outputs:

dataOut — Decoded output data bits, returned as a Boolean scalar.

validOut — Control signal to validate the dataOut, returned as a Boolean scalar.

diagBus — Status signal with diagnostic outputs, returned as a bus signal.

Receiver Structure

The OFDM Receiver subsystem performs a set of operations in a sequence. This subsystem uses the whdlOFDMRx reference model. The top-level subsystem mask of the reference model initializes the model using the whdlexamples.OFDMRxParameters function. The following figure shows the contents inside the top-level subsystem in the reference model.

Decimation Filter Chain

The Decimation Filter Chain subsystem decimates the input by a factor of 16 resulting in the waveform with a rate of 1.92 Msps. The CIC Decimator , FIR Decimator, and Discrete FIR Filter blocks are used for decimation process.

Synchronization and OFDM Demodulation

The Synchronization and OFDM Demodulation subsystem performs frequency and time synchronization and OFDM demodulation.

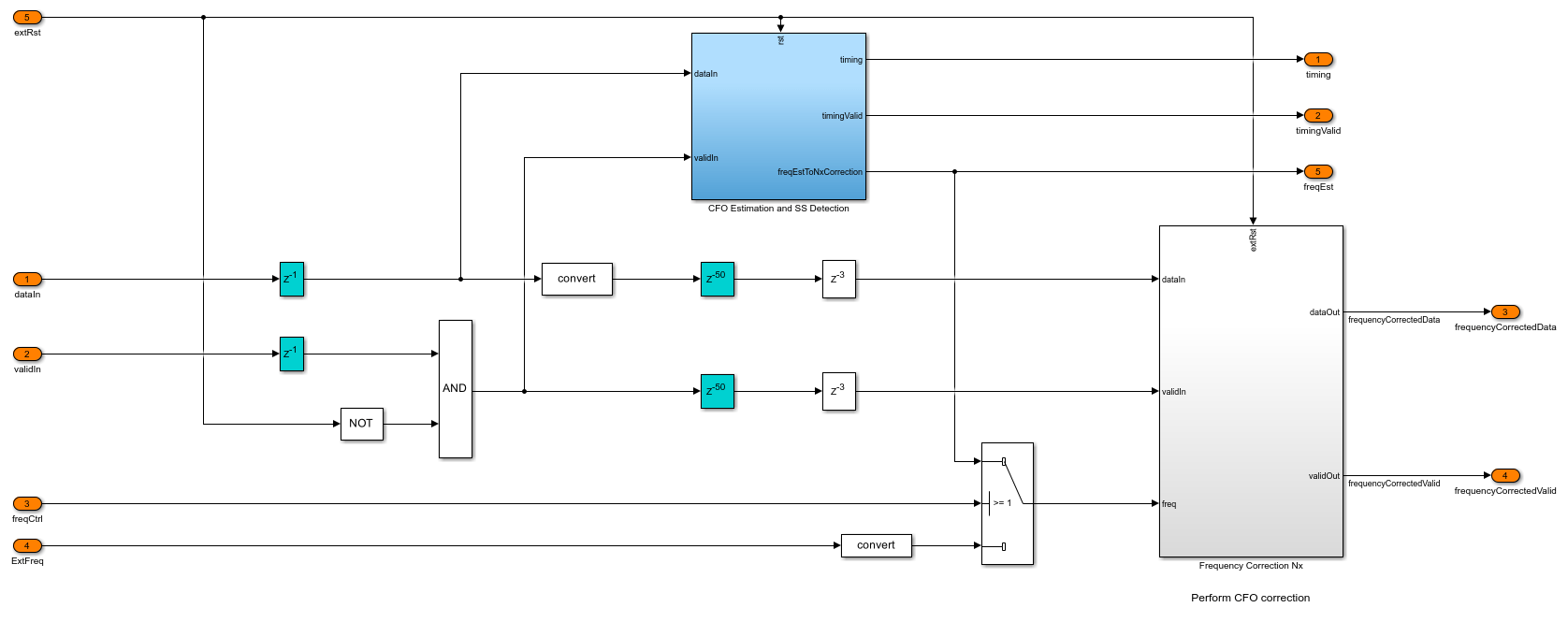

The Frequency and Time Synchronization subsystem comprises Timing Adjust and CFO Estimation and Correction and SS Detection subsystems.

The CFO Estimation and Correction and SS Detection subsystem comprises CFO Estimation and SS Detection subsystem, and Frequency Correction Nx subsystem, which performs frequency correction for the input signal. The estimate from the CFO Estimation and SS Detection subsystem is used for frequency correction if the frequencyOffsetCorrectionType signal on the top-level model interface is set to Use internally estimated frequency offset. The externalFrequencyOffset is used for frequency correction if the frequencyOffsetCorrectionType signal is set to Use externally provided frequency offset.

The CFO Estimation and SS Detection subsystem comprises CFO Estimation, Start Controller, Sync Signal Search, and Frequency Correction 1x subsystems.

The CFO Estimation subsystem uses the cyclic prefix correlation technique to estimate the CFO of the input signal. The CyclicPrefixCorrelator subsystem estimates one CFO value for every six OFDM symbols by averaging all the estimates in six OFDM symbols. The AngleAtMaximum subsystem selects the strongest correlation peak for every six OFDM symbols and records its phase angle. The AngleFilter subsystem implements an averaging filter to average all the recorded phase angles for a duration of 12 ms. The resulting phase angle serves as a final CFO estimate.

The Sync Signal Search subsystem implements the SS correlation. SS detection is performed by continuously cross-correlating the received signal with the SS signal in the time domain. In addition, the energy of the signal in the span of the correlator is computed on each time step and then scaled to generate a threshold. The Max Peak Searcher subsystem begins searching for the maximum correlation peak after 12 ms and searches for every 3 ms time window. The subsystem records the timing offset of the synchronization. The Start Controller function block notifies the Max Peak Searcher when the 12 ms duration is ended.

The timing offset recorded at the maximum correlation value by the Max Peak Searcher subsystem is transferred to the Timing Adjust subsystem to synchronize timing.

The OFDM Demodulator block demodulates the synchronized samples and generates subcarriers.

Channel and CPE Estimation and Correction

The Channel and CPE Estimation and Correction subsystem estimates the channel frequency response, equalizes the channel, performs CPE estimation, and corrects the CPE.

The Reference Signal Parsing MATLAB function block separates the OFDM symbols reserved for computing channel estimates.

The OFDM symbols reserved for computing channel estimates are streamed through Channel Estimation subsystem. The OFDM Channel Estimator block averages the estimates from the two symbols and outputs the final channel estimates. The estimates are streamed into the Channel Equalization subsystem that stores the estimates in a RAM and performs frequency-domain channel equalization using the OFDM Equalizer block for all the remaining OFDM symbols in the frame.

The Header and Data Parsing MATLAB function block separates the OFDM symbols corresponding to header and data symbols.

The frequency domain channel-equalized data subcarriers stream through the Common Phase Error Estimation and Correction subsystem. In the frequency estimation process, there is always an estimation error. This estimation error results in a residual frequency offset in the channel-equalized subcarriers. This results a CPE in all the subcarriers in an OFDM symbol and changes from symbol to symbol. The CPE Estimation subsystem estimates the CPE on each OFDM symbol using the 12 pilot subcarriers. The pilots are the known subcarriers and any phase rotation in the received symbols is estimated by using the pilots. The estimates drawn from the same symbol are averaged to get the final estimate. The symbol is stored in the Symbol Buffer MATLAB function block during estimation. Once the estimate is ready, the symbol is read from this buffer block and the CPE Correction subsystem corrects the CPE in the data subcarriers with that estimate.

Header and Data Recovery

The Header and Data Recovery subsystem recovers header information and data bits.

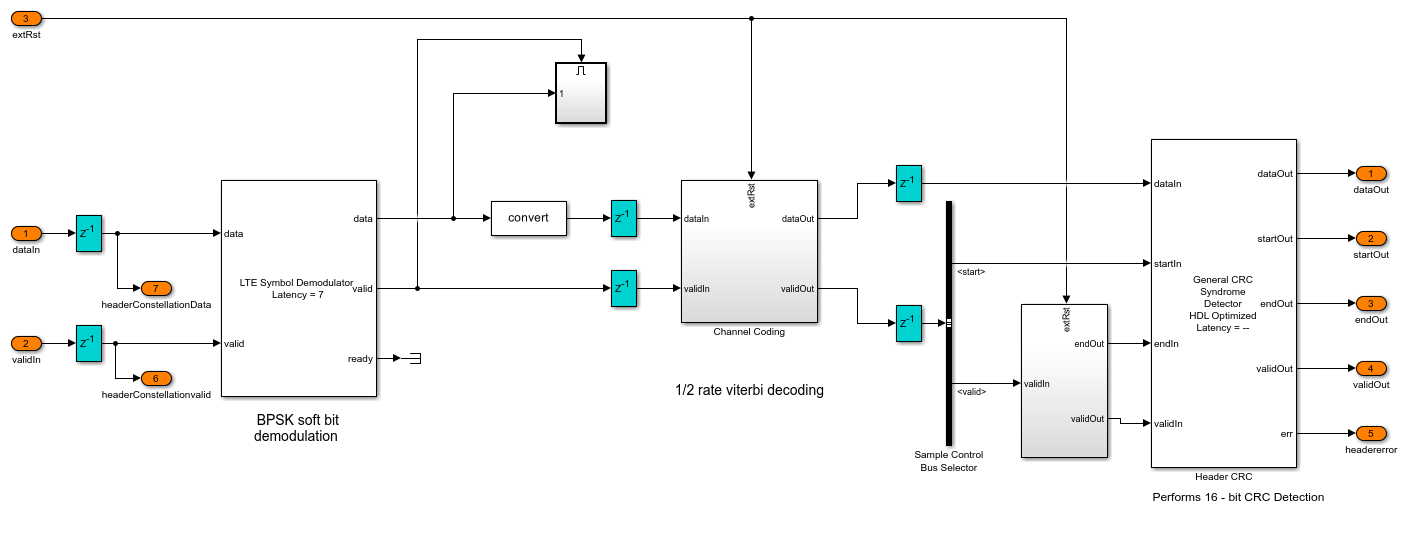

The frequency domain channel-equalized header subcarriers stream into the Header Recovery subsystem. The LTE Symbol Demodulator block performs BPSK soft symbol demodulation. The Channel Coding subsystem is equipped with a Deinterleaver subsystem and Viterbi Decoder block. The Deinterleaver subsystem performs deinterleaving with a maximum block size of 72 and the number of columns as 18. The Viterbi Decoder block performs 1/2 rate viterbi decoding. For more information about the Deinterleaver subsystem, see the HDL Interleaver and Deinterleaver example. The General CRC Syndrome Detector HDL Optimized block uses a 16-bit CRC checksum to validate the decoded bits from the Viterbi Decoder block. If the CRC checksum fails, the General CRC Syndrome Detector HDL Optimized block generates an error signal.

The Data Recovery subsystem uses header information to decode data bits. The header information is stored in the registers. These registers are used to access the header information. The LTE Symbol Demodulator block performs soft bit BPSK, QPSK, 16-QAM, or 64-QAM symbol demodulation associated with the modulation type retrieved from the header information. The Channel Coding subsystem is equipped with the Deinterleaver subsystem, Depuncturer, and Viterbi Decoder blocks. Each code rate is assigned a predefined punctured vector pattern. Based on the code rate retrieved from the header information, the Channel Coding subsystem performs deinterleaving and depuncturing followed by viterbi decoding. The decoded bits are streamed through the Descrambler subsystem. The General CRC Syndrome Detector HDL Optimized block uses a 32-bit CRC checksum to validate the descrambled bits. If the CRC checksum fails, the General CRC Syndrome Detector HDL Optimized block generates an error signal.

Diagnostic Bus Formation

The Diagnostic Bus Formation subsystem creates a bus signal for some status signals of the receiver.You can use this bus signal to analyze the receiver when deployed onto the hardware.

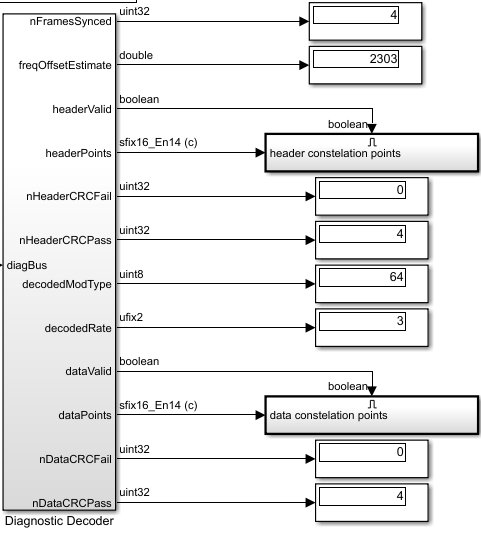

The descrambled bits stream out of the receiver and stored to workspace in the Capture Data Bits subsystem in the top-level receiver model. The Diagnostics Decoder subsystem decodes the source-coded header information and counts the number of synchronized frames, number of header CRC passes and failures, and the number of data CRC passes and failures in the bus signal formed in the Diagnostic Bus Formation subsystem. The Simulink display blocks display the diagnostics decoder information.

Run Receiver

Use the runOFDMReceiverModel script to run the example. This script describes a procedure to initialize, generate inputs, run, and verify the whdlOFDMReceiver model. You can choose a custom transmitter waveform and a channel impairment configuration of your choice in the script.

Alternatively, to run the model, connect the receiver back-to-back with the transmitter in the HDL OFDM Transmitter example and run the Simulink model. For more information on how to connect the transmitter and the receiver Simulink models back-to-back see the HDL OFDM MATLAB References example.

Compare and Verify Results

To compare the output of the Simulink model with the whdlexamples.OFDMRx MATLAB function, set the CompareWithMATLABReference variable in the runOFDMReceiverModel script to true and then run the script.

>> runOFDMReceiverModel

Running Simulink OFDM Rx ...

### Searching for referenced models in model 'whdlOFDMReceiver'.

### Found 1 model reference targets to update.

### Starting serial model reference simulation build.

### Successfully updated the model reference simulation target for: whdlOFDMRx

Build Summary

Model reference simulation targets:

Model Build Reason Status Build Duration

=======================================================================================================

whdlOFDMRx Target (whdlOFDMRx_msf.mexw64) did not exist. Code generated and compiled. 0h 8m 58.219s

1 of 1 models built (0 models already up to date)

Build duration: 0h 9m 32.112s

Number of header CRC failed = 0 per 4

Number of bit errors = 0 per 15208

Running MATLAB OFDM Rx ...

Estimating carrier frequency offset ...

First four frames are used for carrier frequency offset estimation.

Estimated carrier frequency offset is 2.298301e+03 Hz.

Detected and processing frame 5

------------------------------------------

Header CRC passed

Modulation: BPSK, codeRate=5/6 and FFT Length=128

Data CRC passed

Data decoding completed

------------------------------------------

Detected and processing frame 6

------------------------------------------

Header CRC passed

Modulation: QPSK, codeRate=3/4 and FFT Length=128

Data CRC passed

Data decoding completed

------------------------------------------

Detected and processing frame 7

------------------------------------------

Header CRC passed

Modulation: 16QAM, codeRate=2/3 and FFT Length=128

Data CRC passed

Data decoding completed

------------------------------------------

Detected and processing frame 8

------------------------------------------

Header CRC passed

Modulation: 64QAM, codeRate=1/2 and FFT Length=128

Data CRC passed

Data decoding completed

------------------------------------------

Comparison between Simulink and MATLAB Rx ...

Signal SQNRdB (real) SQNRdB (imaginary)

____________________________________ _____________ __________________

Decimation filter chain output 57.81 57.794

Estimated frequency offset 65.116 NaN

SS correlator output 50.525 NaN

SS threshold output 44.061 NaN

Frequency and time synchronized data 32.427 32.76

OFDM demodulator output 29.816 34.207

Channel equalized data 35.097 34.455

Header constellation points 34.287 36.744

Data constellation points 34.201 34.696

Data soft llr points 32.442 NaN

You can see the constellation plot on the constellation scope. The scopes can be activated by using the Control Scope button in the whdlOFDMReceiver model.

Generate HDL Code

To generate the HDL code for this example, you must have an HDL Coder™ license. Run the whdlexamples.OFDMRxSimulink function and use makehdl and makehdltb commands to generate HDL code and HDL testbench for the OFDM Receiver subsystem. The testbench generation time depends on the simulation time.

You can synthesize the generated HDL code and target on the Xilinx® Zynq®-7000 ZC706 evaluation board. The table shows the post place and route resource usage results. The maximum frequency of operation is 217 MHz.

Resources Usage

_______________ _____

Slice LUT 33118

Slice Registers 35784

RAMB36 22

RAMB18 14

DSP48 114

See Also

Blocks

- LTE Symbol Demodulator | Depuncturer | Viterbi Decoder | General CRC Syndrome Detector HDL Optimized | OFDM Demodulator | OFDM Channel Estimator