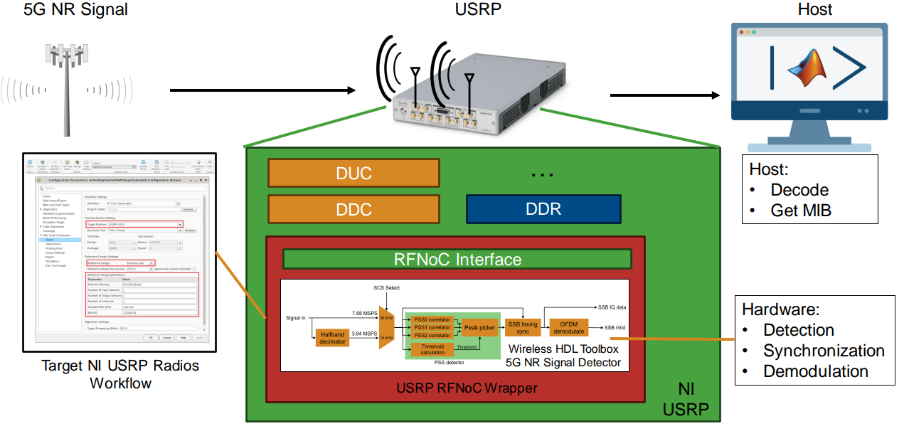

Target NI USRP Radios

Prototype and test SDR algorithms on NI™

USRP™ radio hardware

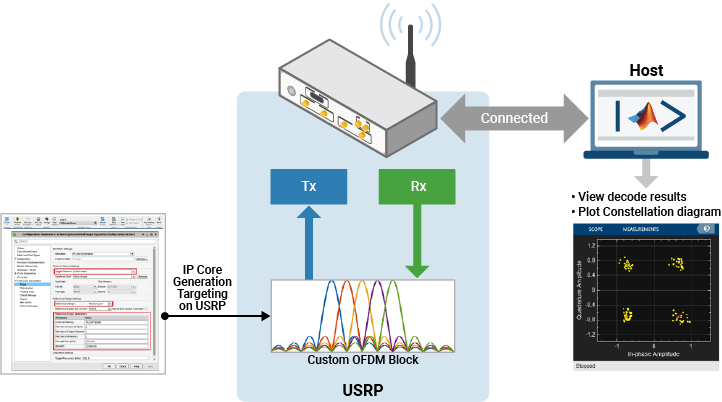

Deploy custom software-defined radio (SDR) algorithms on the FPGA of an NI USRP radio using a Simulink® workflow. Run and verify your design using MATLAB® objects and functions.

Objects

Functions

Topics

- Installation for Targeting NI USRP Radios

Install and configure additional support packages and third-party tools.

- Target NI USRP Radios Workflow

Prototype and deploy SDR algorithms on the FPGA of an NI USRP radio.

- STEP 1: Verify Radio Connection

- STEP 2: Set Up Third-Party Tools

- STEP 3: Prepare Hardware Model for Deployment

- STEP 4: Generate HDL Code

- STEP 5: Generate Bitstream and Program FPGA

- STEP 6: Run and Verify Hardware Implementation

- Supported Radio Devices

Determine which NI USRP radios you can target with Wireless Testbench™.

- System Requirements

Determine the host system requirements for targeting NI USRP radios.