Reuse of Simulink Components Within Chip-Level Design and Verification Environments

Simone Saracino, STMicroelectronics

Diego Alagna, STMicroelectronics

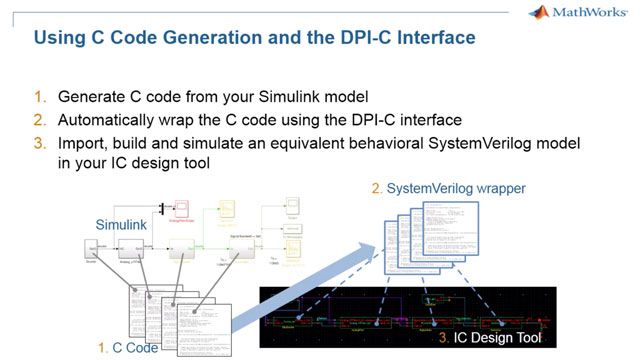

To keep pace with market needs for performance and cost efficiencies, the architecture of integrated circuits (ICs) needs to be highly optimized. Many semiconductor engineering teams are using Simulink® as their main tool to perform such optimizations, since it allows them to easily model and simulate multidomain systems, including analog and digital components. Moreover, this approach enables verification activities within Simulink, before the implementation phase has started, allowing engineers to find bugs early and shorten lead times. In this presentation, you will learn how Simulink design models and testbenches can be reused throughout the IC design cycle. We will demonstrate how design models can be converted to synthesizable RTL through HDL code generation and how Simulink verification components can be reused within UVM verification environments, avoiding duplication of effort between system-level activities (performed within Simulink) and RTL-level activities (performed using EDA tools).

Published: 30 May 2022