外部组件接口

集成自定义 HDL 代码和供应商特定 AMD 或 Intel 模块等外部组件

HDL Coder™ 允许您将自定义 HDL 代码和供应商特定模块等外部组件集成到设计中。

使用 DocBlock 模块将自定义 HDL 代码添加到设计并创建一个黑盒接口。该黑盒接口允许您为现有手动编写的 HDL 代码、第三方 IP 或 HDL Coder 生成的代码创建一个接口。

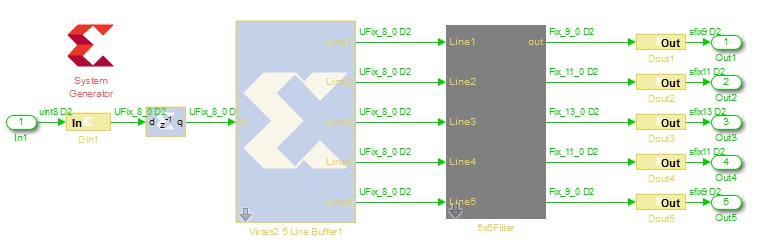

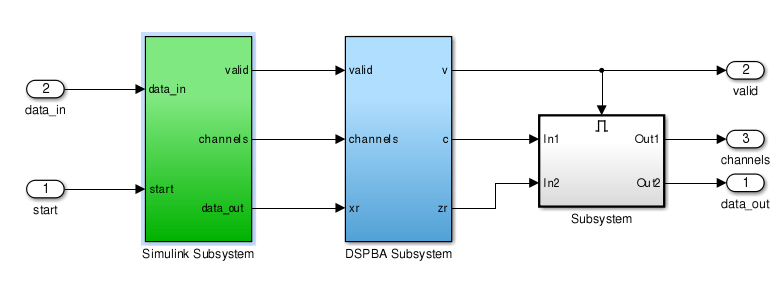

使用性能优化的 AMD® 或 Intel® 模块构建模型并生成集成的 HDL 代码。利用 AMD Vitis Model Composer 或 DSP Builder for Intel FPGAs 等第三方工具及 HDL Coder,在设计中将各种供应商特定 HDL 模块与 Simulink® 模块集成。

主题

常规

- Pass-Through and No-Op Implementations

Bypassing or omitting selected subsystems in generated code.

外部 HDL 代码

- Integrate Custom HDL Code by Using DocBlock

Integrate custom HDL code using the DocBlock block. - Generate Black Box Interface for Subsystem

How to generate an interface to existing or legacy HDL code from a subsystem. - Generate Black Box Interface for Referenced Model

Specify a black box implementation for the Model block when you already have legacy or manually-written HDL code. - Specify Bidirectional Ports

Specify bidirectional ports for a black box. - Customize Black Box or HDL Cosimulation Interface

How to use block implementation parameters to control generation and naming of ports and other attributes of the generated interface. - Generate Cosimulation Model

Automatically generate a Simulink model that cosimulates with your HDL simulator.

第三方工具

- Generate Code for AMD Blocks by Using AMD Vitis Model Composer

Generate HDL code for the model that contains AMD blocks by using AMD Vitis Model Composer. (自 R2025a 起) - Create an Altera DSP Builder Subsystem

Code generation from a model using both Altera® DSP Builder and HDL Coder.