Microchip FPGA 和 SoC 器件

生成 HDL 代码和嵌入式软件并部署到 Microchip SoC 器件上

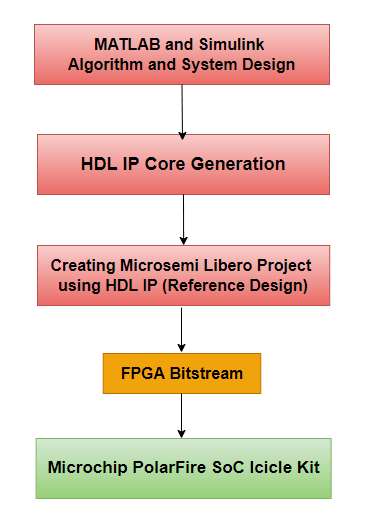

HDL Coder™ 可以生成 IP 核,将其集成到 Libero® 工程中,并对 Microchip 硬件进行编程。要将设计部署到 Microchip FPGA 和 SoC 器件,您必须安装 HDL Coder Support Package for Microchip FPGA and SoC Devices。有关安装信息,请参阅HDL Coder 支持的硬件。

HDL Coder Support Package for Microchip FPGA and SoC Devices 支持生成可集成到使用 Microchip Libero Design Suite 的 FPGA 设计中的 IP 核。

此支持包包括常见 Microchip 开发工具包的参考设计,因此您可以生成 HDL 代码,到 I/O 及 AXI 寄存器的端口映射,以及与 DDR 内存的对接。它还支持 HDL Coder 自定义参考设计 API 以便为基于 Microchip 器件的各种板开发参考设计。

类别

- 设置和配置

下载并安装支持包以与第三方 EDA 工具和受支持的硬件结合使用

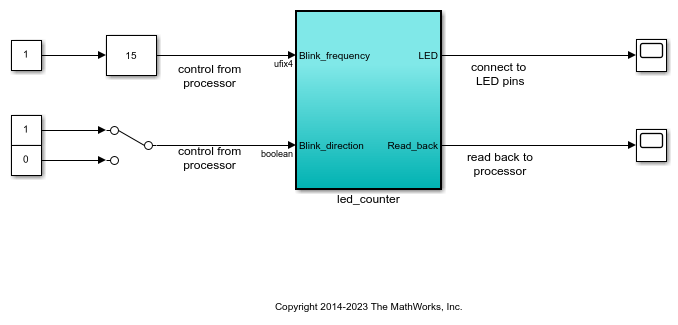

- 自定义 IP 核生成

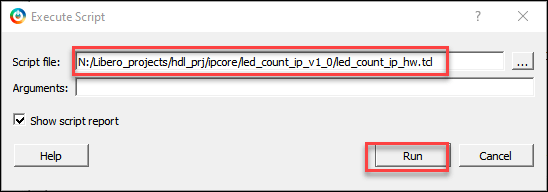

从 DUT 生成 HDL IP 核以部署到默认系统参考设计或注册到板的自定义参考设计

- 自定义板和参考设计

为 Microchip SoC 器件定义和注册自定义参考设计或自定义板

- 部署

创建包含用户编程的比特流并将其下载到 Microchip SoC 平台