原生浮点

HDL Coder™ 原生浮点技术可从浮点设计生成 HDL 代码。以下是一些关键功能:

生成可部署在任何 FPGA 或 ASIC 上的独立于目标的 HDL 代码。

支持完整的 IEEE-754 特征集,包括非规范数、异常和舍入模式。

广泛支持数学和三角函数模块。

与定点设计相比,浮点设计具有更高精度、更宽动态范围和更短开发周期。如果设计包含复杂的数学和三角运算,请使用原生浮点技术。

函数

createFloatingPointTargetConfig | Create floating-point target configuration for floating-point library that you specify |

模块

检查

主题

- Getting Started with HDL Coder Native Floating-Point Support

Learn about the native floating point support in HDL Coder.

- Generate Target-Independent HDL Code with Native Floating-Point

Generate HDL code from floating-point Simulink® models.

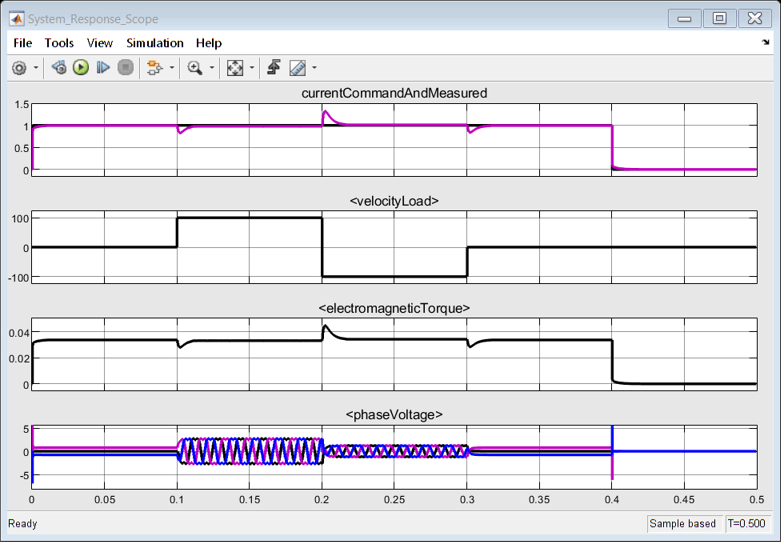

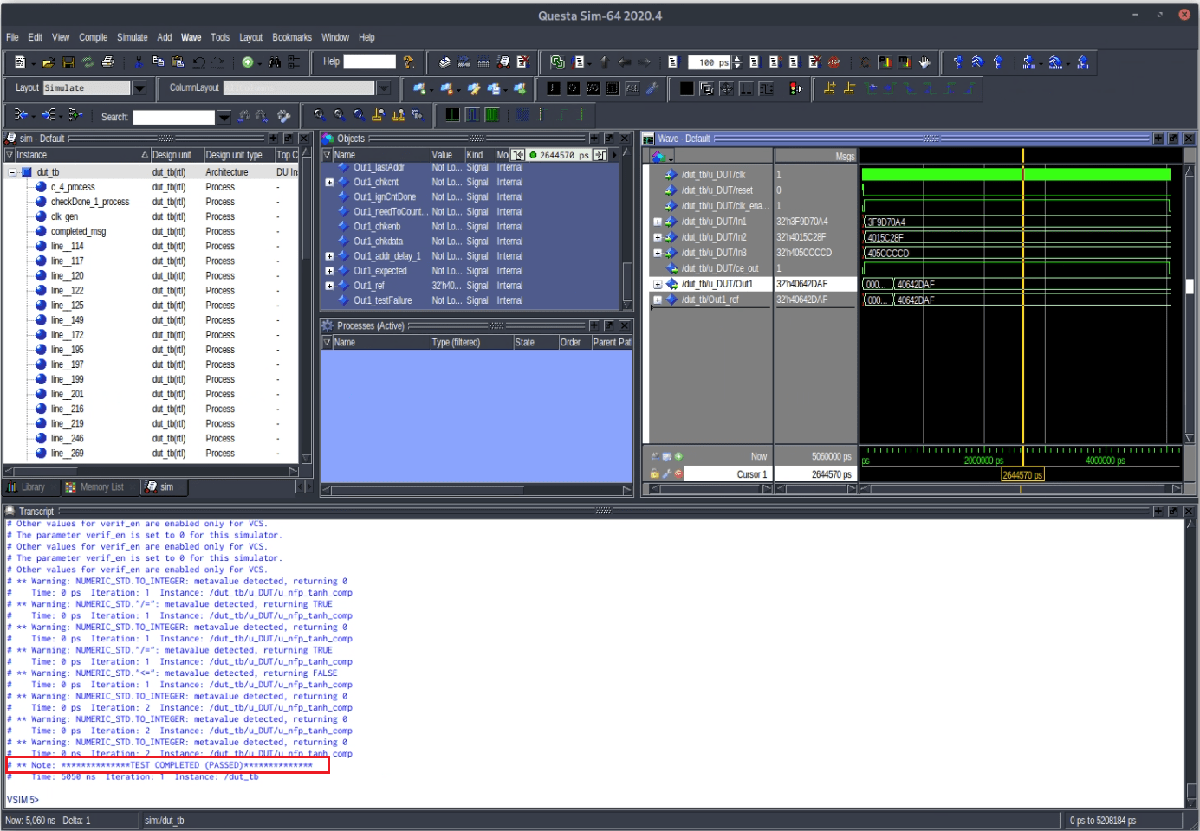

- Verify the Generated Code from Native Floating-Point

How you can verify the generated code from the floating-point model using HDL Testbench, Cosimulation, and FPGA-in-the-loop.

- Numeric Considerations for Native Floating-Point

Learn about nearest even-digit rounding, denormal numbers, exception handling, and relative accuracy and ULP considerations.

- ULP Considerations of Native Floating-Point Operators

ULP considerations, ULP values of native floating-point operators, and adherence to IEEE-754 compliance.

- Latency Considerations with Native Floating Point

Learn how to view the latency of a floating point operator and the various ways to customize it.

- Native Floating Point Support for Simulink Blocks

List of operators and supported blocks in the floating-point model.

- Latency Values of Floating-Point Operators

Latency values of operations supported in native floating-point mode.

- Critical Path Estimation Without Running Synthesis

Find the estimated critical paths in your design without using third-party synthesis tools.

- HDL Block Properties: Native Floating Point

HDL code generation parameters for native floating-point block implementations.

- Synthesis Benchmark of Common Native Floating Point Operators

This example shows how to access and generate synthesis benchmarks for common native floating-point operators with Xilinx® Vivado® and Intel® Quartus® tool.

相关信息

疑难解答

Optimize Generated HDL Code for Multirate Designs with Large Rate Differentials

Causes and possible solutions for fixing HDL code generation issues with multirate models that have large rate differentials.