Generate HDL Code for Simscape Three-Phase PMSM Drive Containing Averaged Switch

This example shows how to generate HDL code and synthesize the results for a three-phase PMSM Simscape™ model that has an averaged switch.

Simscape Models with Averaged Switch

You can generate HDL code for Simscape models with converter blocks that have averaged switches and deploy onto the FPGAs. This example uses a three-phase PMSM model with a six-pulse three-phase controlled converter block consisting of averaged switches. The switching frequency of this model is 50 kHz. For the system to be HDL compatible, the averaged switches use a piecewise constant approximation method for the gate input. Note that this model with the averaged switches might introduce instability during dead time (when all gate inputs are set to 0) with the Partitioning local solver.

Set Up Synthesis Tool Path

If you want to synthesize the generated HDL code, before you use HDL Coder™ to generate code, set up your synthesis tool path. For example, if your synthesis tool is Xilinx® Vivado®, then, install the latest version of Xilinx Vivado as listed in HDL Language Support and Supported Third-Party Tools and Hardware.

Then, set the tool path to the installed Xilinx Vivado executable by using the hdlsetuptoolpath function:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat')

Three-Phase PMSM Drive Model

Open the model from the MATLAB® command prompt.

ModelName = 'ee_pmsm_drive_averaged_switch_hdl';

open_system(ModelName)

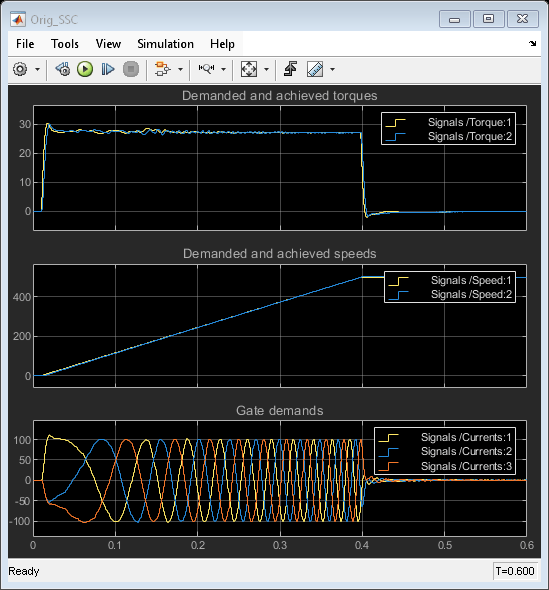

To see how the model works, simulate it.

sim(ModelName)

open_system([ModelName '/Orig_SSC'])

To see the components inside the Simscape Network subsystem, enter:

open_system('ee_pmsm_drive_averaged_switch_hdl/Simscape Network')

For HDL code generation, in the Converter(Three-Phase) block parameter Settings tab, the Integer for piecewise constant approximation of gate input (0 for disabled) parameter value is set to 10. The model is set up to use Partitioning solver by selecting the Use local solver check box in the Solver Configuration (Simscape) block.

Generate HDL Implementation Model

The Simscape HDL Workflow Advisor converts the Simscape plant model to an HDL-compatible implementation model from which you generate HDL code. To generate the HDL implementation model:

1. Open the Simscape HDL Workflow Advisor.

sschdladvisor('ee_pmsm_drive_averaged_switch_hdl')

2. In the Implementation model generation task drop-down list, right-click the Generate implementation model task, then select Run to Selected Task from the list. To get better resource utilization, in the Generate implementation model task window, set Map state space parameter to RAM to On.

After the task passes, you see a link to the HDL implementation model gmStateSpaceHDL_ee_pmsm_drive_averaged_swit.

Generate HDL Code

To modify the configuration parameter values for HDL code generation, navigate to gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem. Right-click the HDL Algorithm subsystem and select HDL Block Properties from the HDL Code list. In the HDL Properties dialog box, set the DistributedPipelining to On. Click Apply and then click OK. Then navigate to the gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem/HDL Algorithm/State Update/Algebraic Clump2/Mode Vector To Index block. Right-click the block and select HDL Block Properties from the HDL Code list. In the HDL Properties dialog box, set the InputPipeline and OutputPipeline parameter values to 2, click Apply and then click OK. Right-click the Multiply State and Multiply F blocks, set the SharingFactor to 8 for the two blocks. Save the model and proceed to the next step.

Set your model configuration parameters to default values recommended for HDL code generation.

hdlsetup('gmStateSpaceHDL_ee_pmsm_drive_averaged_swit')

HDL Workflow Advisor

The HDL Workflow Advisor guides you through the necessary tasks required for generating HDL code and an FPGA design process. It provides you with feedback on the results of each task. When you complete the tasks, you have a synthesis result report from one of the supported synthesis tools.

Open the subsystem HDL Subsystem within the HDL implementation model into the HDL Workflow Advisor.

hdladvisor('gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem')

You can also open the HDL Workflow Advisor from your model window. Right-click the HDL Subsystem and select HDL Workflow Advisor from the list.

Set Target Device and Synthesis Tool

Before you generate HDL code, if you want to deploy the code onto a target platform, specify the synthesis tool.

Open the HDL Workflow Advisor.

Under the Set Target task folder, in the Set Target Device and Synthesis Tool task, specify Target workflow as

Generic ASIC/FPGAand Synthesis tool asXilinx Vivado. The rest of the fields are auto-populated. Specify the Family asKintex7, Device asxc7k325t, Package asfbg676, and Speed as -1.In the Set Target Frequency window, specify the Target Frequency as 150.

Select the task that you want to run and click Run This Task.

HDL Code Generation

In the HDL Code Generation task folder, click Set HDL Options and then click the HDL Code Generation Settings button. This opens the Configuration Parameters dialog box. Select

Adaptive pipeliningunder HDL Code Generation > Optimizations > Pipelining and click Apply.Under the HDL Code Generation > Global Settings > Clock Settings section, set the

Oversampling factorto 300. Click Apply then click OK. To generate HDL code, run the tasks under the HDL Code Generation task folder.

Synthesize Generated HDL Code

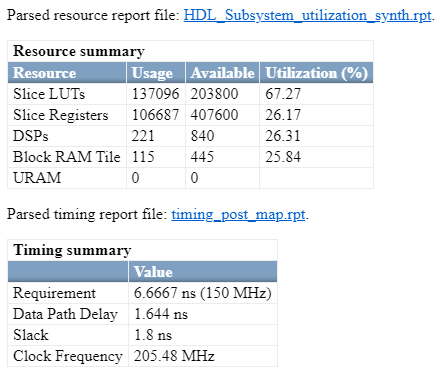

HDL Coder synthesizes the HDL code on the target platform and generates area and timing reports for your design based on the target device that you specify. You can run logic synthesis for a specified FPGA device and get the synthesis reports.

In the FPGA Synthesis and Analysis task folder:

Create an FPGA synthesis project for your supported FPGA synthesis tool.

Start supported FPGA synthesis tools to perform synthesis, mapping, and place/route tasks. To run FPGA synthesis, right-click the Run Synthesis task under the Perform Synthesis and P/R subtask folder. This starts Xilinx Vivado and executes the Vivado Synthesis step. You can annotate your original model with critical path information obtained from the synthesis tools.

See Also

Functions

Topics

- Generate and Validate HDL Code for Simscape Model

- FPGA-Based HIL Deployment of Simscape Model on Speedgoat FPGA I/O Module

- Deploy Simscape Grid Tied Converter Model to Speedgoat IO Module Using HDL Workflow Script

- Generate HDL Code for Nonlinear Simscape Models by Using Partitioning Solver

- Generate HDL Code for Simscape Models by Using Dynamic Switch Approximation