Generate and Manage FPGA I/O Host Interface Scripts

You can use host interface scripts to prototype your algorithms on hardware from MATLAB®. Host interface scripts contains simple MATLAB commands that you can use to connect to your hardware and interact with your algorithm while it runs on hardware. For example, you can tune parameters or capture data for further analysis.

Prerequisites

To run the generated host interface script, you need a hardware board. For instructions on how to set up your hardware board, see Guided Hardware Setup for AMD Boards.

You must have the latest version of the third-party synthesis tool, such as Xilinx® Vivado®. See HDL Language Support and Supported Third-Party Tools and Hardware. In your MATLAB session, set the path to the installed synthesis tool by using the

hdlsetuptoolpathfunction.

Generate Host Interface Scripts

You can generate a host interface script when you generate an IP core using

HDL Coder™. During this process, you must select a host-target interface, which

specifies how MATLAB communicates to your hardware board. To specify the target

interface for the host interface script, in the HDL Code tab,

select Host Interface Script

>

Host target interface and select either

Ethernet or JTAG from the

drop-down menu options. The host-target interface options are:

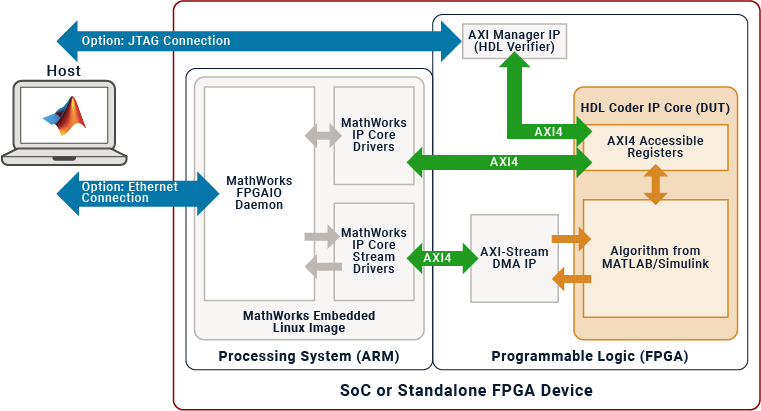

Ethernet — To use the Ethernet option, your target board must have an embedded ARM processor.

JTAG AXI Manager — Use this option for standalone FPGA boards that do not have an embedded ARM processor.

To generate a host interface script by using the Simulink® Toolstrip:

Open the Simulink model and select the design under test (DUT) for which you want to generate an IP core.

Open the HDL Coder tab. In the Apps tab, click HDL Coder.

To use a JTAG interface, in the HDL Code tab, click Settings > Target Settings. Set the Insert AXI Manager (HDL Verifier required) to

JTAG.To generate the host interface script, in the HDL Code tab, click Host Interface Script > Host Interface Script. You can generate the host interface script without generating the IP core. To configure the target interface that the host interface script uses to access the generated IP core, select the Host Interface Script drop-down arrow and set Host target interface to either

JTAGorEthernet. To use the JTAG interface, you must have a HDL Verifier™ license.

To generate a host interface script by using the HDL Workflow Advisor:

Open the Simulink model and select the design under test (DUT) for which you want to generate an IP core.

Open the HDL Coder App.

In the HDL Workflow Advisor, click Task 1.1 Set Target device and Synthesis Tool and configure the target device and synthesis tool.

In 1.2 Set Target Reference Design set the Reference design property. To use the JTAG interface in Task 1.2 Set Target Reference Design, set Insert AXI Manager (HDL Verifier required) to

JTAG.In 1.3 Set Target Interface map your DUT ports to various interfaces. HDL Coder uses these interface settings during host interface script generation.

Click 4.2. Generate Software Interface and select Generate host interface script. Right-click 4.2. Generate Software Interface and select Run to Selected Task.

Host Interface Script Files

When you generate a host interface script file, you create two MATLAB files based on the reference design and target interface table mapping that was configured for your IP core:

Interface script (

gs_<modelName>_interface.m: This script creates anfpgahardware object for interfacing with your FPGA from MATLAB. The interface script contains MATLAB commands that connect to your hardware and program the FPGA, and examples of how to exchange data with your algorithm as it runs on hardware.Interface setup function (

gs_<modelName>_setup.m: This function configures thefpgaobject with the hardware interfaces and ports from your DUT algorithm. The setup function contains DUT port objects that have the port name, direction, data type, and interface mapping information. The function maps these DUT ports to the corresponding interfaces.

Interface Script File

The interface script file creates a connection to your FPGA hardware for reading and writing data. The script file:

Creates an

intelsocorxilinsocobject, which represents a connection to the processor on your hardware board. The script file contains theprogramFPGAcommand that programs the FPGA with the generated bitstream and corresponding device tree. This section is present only when you generate an Ethernet host target interface.Creates an

fpgahardware object that represents a connection to the FPGA on your hardware board.Configures the

fpgaobject with the desired hardware interfaces and ports from your DUT algorithm.Contains commands that read or write data to DUT ports, which you can use to exercise the algorithm running on the hardware. These commands serve only as an example. Update them before running the script to exercise your algorithm.

Releases any hardware resources used by the

fpgaobject to clean up the connection.

Setup Function File

The setup function file configures your fpga object with the

same interfaces as your generated IP core. The setup script is a reusable file.

When you make changes to the IP core, you must update or re-generate the setup

script. This image shows the ports and interface mapping of the DUT and the

setup script and how they are related.

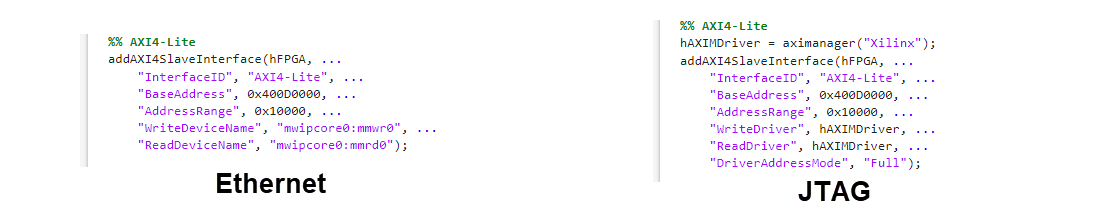

The setup function file changes based on whether the target interface is

Ethernet or JTAG. When you set the target interface to JTAG, HDL Coder uses the aximanager hardware object as the read

and write driver for communicating with AXI registers in your design. This image

shows a comparison between the setup function for the Ethernet and JTAG

interfaces.

Use the Host Interface Script with Hardware

For rapid prototyping, customize the host interface script based on how you modify your original design. After you generate the host interface scripts:

Connect your host computer to the target hardware board using either Ethernet or JTAG.

Modify the read and write commands in the interface script file to match your data requirements. Use the modified script interface with your deployed DUT IP core or algorithm running on the target board.

Run the sections of the host interface script to connect to your hardware board, program the FPGA, create an

fpgaobject, and set up the interfaces. The interfaces are set up based on the interface setup function file. You need to run these sections only once.Run the modified read and write commands and keep iterating on these commands. You can use the MATLAB command line to run specific commands.

Release the connection to the hardware board after completing your prototyping.

This image shows how to use the host interface script and the relation between the steps and the interface script file.

After you have iterated and tested the host interface script, you can :

Integrate the script into a testing or verification workflow.

Create a live script and interactive prototype your design. For example, see Prototype Generated IP Core on Hardware using FPGA I/O.

Manage Host Interface Scripts

You can manage your host interface script files by either updating or re-generating the files. Update host interface script files when you make minor changes such as modifying existing parameters, making minor error fixes, and so on. Re-generate host interface script files when making major changes such as modifying the DUT port mappings, changing the target hardware device vendor, changing the target software tool, and so on. When you re-generate the host interface script files, HDL Coder displays a warning about overwriting the existing files. You can rename your existing files to prevent them from being overwritten.