Improve Resource Sharing with Clone Detection and Replacement

This example shows how you can automatically identify and replace recurring patterns by using the Clone Detector (Simulink Check) app. Consequently, it also improves opportunities for optimizing the model by using resource sharing. The Clone Detector app refactors models by identifying clones in a design and replacing clones with links to subsystem blocks in a library. This example uses a model that has already been modified for optimal resource sharing by using the Clone Detector app. To learn more about these modifications, see Improve Resource Sharing with Design Modifications.

Clone Detection

Clone Detection is a tool that can be used to identify modeling patterns in a design that are similar to a few sample patterns provided as inputs through a custom library file. Once the Clone Detector app identifies these patterns, it replaces the patterns with atomic subsystems. This enables the generation of optimal code through code reuse and results in better resource utilization through sharing of resources among the atomic subsystems. For more information regarding Clone Detection, see Enable Component Reuse by Using Clone Detection (Simulink Check).

Set Up Model for Resource Sharing

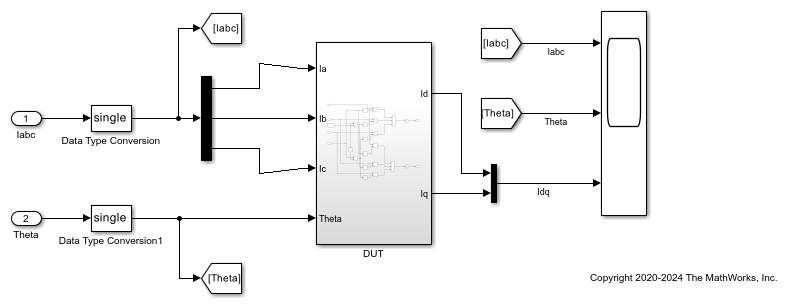

The edited model is saved as hdlcoderParkTransformShare.slx. Copy this version of the model into the temporary directory using these commands:

design_name = 'hdlcoderParkTransformShare'; design_new_name = 'hdlcoderParkTransformShareCopy'; copyfile(fullfile([design_name,'.slx']), fullfile([design_new_name,'.slx']), 'f'); % Open the model. open_system(design_new_name);

Set the block property SharingFactor to 6 on the subsystem of interest and generate HDL along with the corresponding reports from the model.

subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 6); save_system(design_new_name); makehdl(subsystem);

### Working on the model hdlcoderParkTransformShareCopy ### Generating HDL for hdlcoderParkTransformShareCopy/DUT ### Using the config set for model hdlcoderParkTransformShareCopy for HDL code generation parameters. ### Running HDL checks on the model 'hdlcoderParkTransformShareCopy'. ### Begin compilation of the model 'hdlcoderParkTransformShareCopy'... ### Working on the model 'hdlcoderParkTransformShareCopy'... ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 38 cycles. ### Output port 2: 38 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_hdlcoderParkTransformShareCopy'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx ### Delay absorption obstacles can be diagnosed by running this script: hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption.m ### To clear highlighting, click the following MATLAB script: hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m ### Generating new validation model: 'gm_hdlcoderParkTransformShareCopy_vnl'. ### Validation model generation complete. ### Begin VHDL Code Generation for 'hdlcoderParkTransformShareCopy'. ### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 6. ### Begin VHDL Code Generation for 'DUT_tc'. ### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_tc.vhd. ### Code Generation for 'DUT_tc' completed. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sincos_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sincos_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sub_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_add_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single_block.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_uminus_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_uminus_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT.vhd. ### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_pkg.vhd. ### Code Generation for 'hdlcoderParkTransformShareCopy' completed. ### Generating HTML files for code generation report at index.html ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'hdlcoderParkTransformShareCopy' complete with 0 errors, 0 warnings, and 2 messages. ### HDL code generation complete.

The generated High-level Resource Report shows that the resource utilization for the design was estimated to be:

Multipliers | 13 |

Adders/Subtractors | 175 |

Registers | 1053 |

Total 1-Bit Registers | 14097 |

RAMs | 0 |

Multiplexers | 601 |

I/O Bits | 196 |

Static Shift operators | 15 |

Dynamic Shift operators | 8 |

You can also run synthesis workflow on the model. The synthesis results for this model are:

Resource | Usage | Available | Utilization (%) |

Slice LUTs | 8470 | 303600 | 2.79 |

Slice Registers | 8510 | 607200 | 1.40 |

DSPs | 13 | 2800 | 0.46 |

Block RAM Tile | 0 | 1030 | 0.00 |

URAM | 0 | 0 | 0 |

For more details regarding synthesis workflow, see HDL Code Generation and FPGA Synthesis from Simulink Model.

Use Clone Detection to Optimize the Model for Resource Sharing

Before you use the Clone Detector app, create a custom library that contains each repeating pattern in the model as an Atomic Subsystem. For this example, you have a custom library called hdlcoderParkTransformShareLib.slx.

% Copy the library into the temporary directory lib_name = 'hdlcoderParkTransformShareLib'; lib_new_name = 'hdlcoderParkTransformShareLibCopy'; copyfile(([lib_name,'.slx']), fullfile([lib_new_name,'.slx']), 'f'); % Open the custom library open_system('hdlcoderParkTransformShareLibCopy');

Replace patterns of the model with the library containing the Atomic Subsystem. To configure the Clone Detector app and replace the clones, refer to Enable Component Reuse by Using Clone Detection (Simulink Check). Specifically, follow the instructions in the Set the Parameters for Clone Detection section to link the library for clone detection, and set the Maximum number of unmatched block parameters value to 0.

Then, follow the Replace Clones section to apply this library to the model for exact clone replacement.

Notice that all the patterns in the original model has been replaced with atomic subsystems from the library as shown below:

<<../hdlcoderParkTransform_result_model.PNG>>

Save the changes made to this system. In the Simulink Editor, on the Simulation tab, click Save.

Compare Results from Optimized Model

Since this model contains the Sin, Cos, and Product blocks inside atomic subsystems, they can now be shared and results in an improvement in resource utilization.

subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 3); % Generate HDL code and the corresponding reports for the optimized model makehdl(subsystem);

### Working on the model hdlcoderParkTransformShareCopy ### Generating HDL for hdlcoderParkTransformShareCopy/DUT ### Using the config set for model hdlcoderParkTransformShareCopy for HDL code generation parameters. ### Running HDL checks on the model 'hdlcoderParkTransformShareCopy'. ### Begin compilation of the model 'hdlcoderParkTransformShareCopy'... ### Working on the model 'hdlcoderParkTransformShareCopy'... ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 32 cycles. ### Output port 2: 32 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_hdlcoderParkTransformShareCopy'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx ### Delay absorption obstacles can be diagnosed by running this script: hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption.m ### To clear highlighting, click the following MATLAB script: hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m ### Generating new validation model: 'gm_hdlcoderParkTransformShareCopy_vnl'. ### Validation model generation complete. ### Begin VHDL Code Generation for 'hdlcoderParkTransformShareCopy'. ### MESSAGE: The design requires 3 times faster clock with respect to the base rate = 6. ### Begin VHDL Code Generation for 'DUT_tc'. ### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_tc.vhd. ### Code Generation for 'DUT_tc' completed. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sincos_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sincos_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sub_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_add_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT/nfp_uminus_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_uminus_single.vhd. ### Working on hdlcoderParkTransformShareCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT.vhd. ### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_pkg.vhd. ### Code Generation for 'hdlcoderParkTransformShareCopy' completed. ### Generating HTML files for code generation report at index.html ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'hdlcoderParkTransformShareCopy' complete with 0 errors, 0 warnings, and 2 messages. ### HDL code generation complete.

After sharing, the High-level Resource Report shows that the resource utilization for the design was estimated to be:

Resource Usage

_________________________ ________

Multipliers 13

Adders/Subtractors 177

Registers 1004

Total 1-Bit Registers 16657

RAMs 0

Multiplexers 610

I/O Bits 196

Static Shift operators 8

Dynamic Shift operators 8

Notice that the Adders/Subtractors, Registers, and Total 1-Bit Registers counts have reduced after the atomic subsystems are shared.

You can also run synthesis workflow on the model. The synthesis results for this model are:

Resource Usage

_________________________ ________

Slice LUTs 8848

Slice Registers 8308

DSPs 13

Block Ram Tile 0

URAM 0

Notice that the Slice Registers count has reduced after sharing.