Improve Resource Sharing with Design Modifications

This example shows how to improve opportunities for resource sharing to optimize your model design by making certain modifications to your design. Resource sharing is an HDL Coder optimization that improves area utilization in the design on the target FPGA device. The optimization identifies multiple functionally equivalent resources and replaces them with a single resource. For more information, see Resource Sharing.

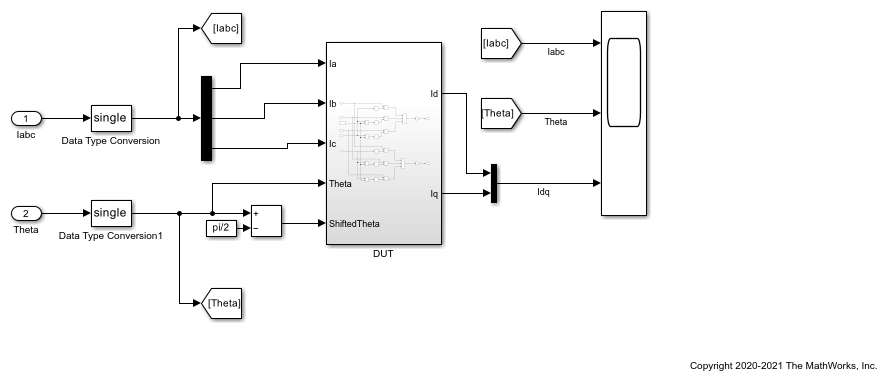

Analyze the Current Model

Execute the following lines of code to copy the necessary example files into a temporary folder.

design_name = 'hdlcoderParkTransform'; design_new_name = 'hdlcoderParkTransformCopy'; copyfile(fullfile([design_name,'.slx']), fullfile([design_new_name,'.slx']), 'f'); % Open the model. open_system(design_new_name);

% Set a SharingFactor of 6 on the subsystem of interest and generate % HDL along with the corresponding reports from the model. subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 6); makehdl(subsystem);

### Working on the model <a href="matlab:open_system('hdlcoderParkTransformCopy')">hdlcoderParkTransformCopy</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderParkTransformCopy/DUT')">hdlcoderParkTransformCopy/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderParkTransformCopy', { 'HDL Code Generation' } )">hdlcoderParkTransformCopy</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderParkTransformCopy'.

### Begin compilation of the model 'hdlcoderParkTransformCopy'...

### Working on the model 'hdlcoderParkTransformCopy'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 42 cycles.

### Output port 2: 42 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderParkTransformCopy', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderParkTransformCopy'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformCopy/gm_hdlcoderParkTransformCopy.slx')">hdl_prj/hdlsrc/hdlcoderParkTransformCopy/gm_hdlcoderParkTransformCopy.slx</a>

### Begin VHDL Code Generation for 'hdlcoderParkTransformCopy'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 1e-05.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sin_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sin_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sub_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_mul_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_mul_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add2_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add2_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sub_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_pkg.vhd.

### Code Generation for 'hdlcoderParkTransformCopy' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy', '/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_report.html

### HDL check for 'hdlcoderParkTransformCopy' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

In the generated Streaming and Sharing report, notice that there are specific groups that were identified to be eligible for sharing:

Resource Type Group Size Block Name

_________________ ____________ ____________

Trigonometry 6 sine

Sum 2 AddSub2

Sum 2 AddSub1

Product 6 Product

Product 2 GainThe Native Floating-Point Resource Report shows the operators needed:

Resource Usage

_________________________ ________

Adders 4

Multipliers 2

Sin 1

Subtractors 2The High-level Resource Report shows that the resource utilization for the design was estimated to be:

Resource Usage

_________________________ ________

Multipliers 9

Adders/Subtractors 152

Registers 1121

Total 1-Bit Registers 15896

RAMs 0

Multiplexers 857

I/O Bits 228

Static Shift operators 5

Dynamic Shift operators 13You can also run synthesis workflow on the model. The synthesis results for this model are:

Resource Usage

_________________________ ________

Slice LUTs 29381

Slice Registers 24140

DSPs 50

Block Ram Tile 0

URAM 0For more details regarding synthesis workflow, see HDL Code Generation and FPGA Synthesis from Simulink Model.

Detect Patterns in Model

Upon further analysis of the model, you can see that there are a few patterns that can be modified to improve resource sharing.

The first such pattern is with the Add and Subtract blocks whose names start with AddSub and whose output goes to Sin blocks.

The second pattern corresponds to a Sum (as an addition or subtraction) block followed by a Gain block.

In both of these patterns, there are some dissimilarities in the highlighted blocks that prevent resource sharing from happening optimally. The dissimilarities are as follows:

First, the signs of the Sum blocks in the region near the Gain blocks are different. Going from top to bottom, the signs are +++ and ---.

You can fix this inconsistency with the following changes:

Switch the signs of the bottom Sum block from

---to+++Make the three bottom Sin blocks to Cos blocks.

Change the input to the Cos block and the two bottom Sum blocks from

Inport 5 ShiftedThetatoInport 4 Theta.

Second, the signs of the Sum blocks in the different regions are different. Going from the top to bottom, the signs are +-, ++, +- and ++.

The blocks with both positive signs are being shared separately from the blocks with alternating signs. This separation between the blocks with both positive signs and the blocks with alternating signs requires more resources. You can simplify your model further to reduce the number of Sum blocks in your model while improving resource sharing. The input to the Sum blocks are the same, and you can reduce the number of Sum blocks you need to two. Then, the inconsistency between the signs is easily fixed by introducing a Unary Minus block.

The discrepancy is then resolved, and this model now shares more resources than the original.

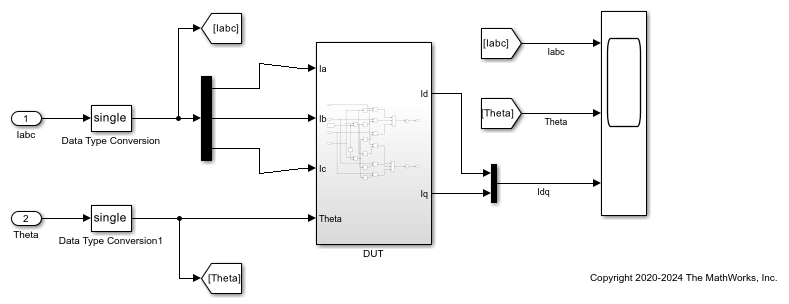

This edited model is saved as hdlcoderParkTransformShare.slx. Copy this version of the model into the temporary directory using the following commands:

design_name = 'hdlcoderParkTransformShare'; design_new_name = 'hdlcoderParkTransformShareCopy'; copyfile(fullfile([design_name,'.slx']), fullfile([design_new_name,'.slx']), 'f'); % Open the model. open_system(design_new_name);

Compare Results from Optimized Model

Since this model has been improved for resource sharing, more blocks are shared and results in an improvement in resource utilization. Set a SharingFactor of 3 on the subsystem of interest and generate HDL along with the corresponding reports from the optimized model

subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 6); makehdl(subsystem);

### Working on the model <a href="matlab:open_system('hdlcoderParkTransformShareCopy')">hdlcoderParkTransformShareCopy</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderParkTransformShareCopy/DUT')">hdlcoderParkTransformShareCopy/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderParkTransformShareCopy', { 'HDL Code Generation' } )">hdlcoderParkTransformShareCopy</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderParkTransformShareCopy'.

### Begin compilation of the model 'hdlcoderParkTransformShareCopy'...

### Working on the model 'hdlcoderParkTransformShareCopy'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 38 cycles.

### Output port 2: 38 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderParkTransformShareCopy', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderParkTransformShareCopy'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy_vnl')">gm_hdlcoderParkTransformShareCopy_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderParkTransformShareCopy'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 6.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sincos_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sincos_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sub_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_add_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single_block.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_uminus_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_uminus_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_pkg.vhd.

### Code Generation for 'hdlcoderParkTransformShareCopy' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy', '/tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1586773/tp309ca78f/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_report.html

### HDL check for 'hdlcoderParkTransformShareCopy' complete with 0 errors, 0 warnings, and 2 messages.

### HDL code generation complete.

After making those design modifications, the Native Floating-Point Resource Report shows the updated operators needed:

Resource Usage

_________________________ ________

Adders 2

Multipliers 2

SinCos 1

Subtractors 1

Unary Minus 1Notice that the Adders, Multipliers, and Subtractors count have reduced after sharing.

After sharing, the High-level Resource Report shows that the resource utilization for the design was estimated to be:

Resource Usage

_________________________ ________

Multipliers 13

Adders/Subtractors 178

Registers 1012

Total 1-Bit Registers 16888

RAMs 0

Multiplexers 610

I/O Bits 196

Static Shift operators 8

Dynamic Shift operators 8After running synthesis on the model, you can see the following results:

Resource Usage

_________________________ ________

Slice LUTs 8792

Slice Registers 8419

DSPs 13

Block Ram Tile 0

URAM 0Notice that the Slice LUTs, Slice Registers, and DSPs counts have reduced after sharing.

To learn how you can further improve resource sharing with automatically replacement of recurring patterns using the Clone Detection application, see Improve Resource Sharing with Clone Detection and Replacement.