验证

使用 HDL 测试平台、联合仿真或 FPGA 在环对生成的 HDL 代码进行仿真和验证

您可使用 HDL 测试平台、联合仿真(需要 HDL Verifier™)或 FPGA 在环(需要 HDL Verifier)验证生成的代码。

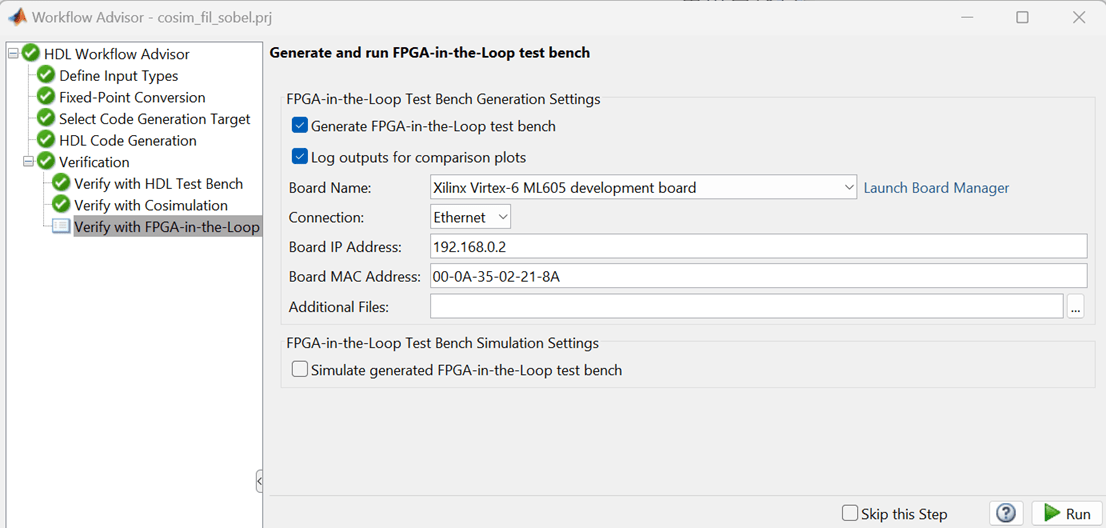

通过 FPGA 在环 (FIL) 仿真,您可以使用与此软件严格同步的 FPGA 板运行 Simulink® 或 MATLAB® 仿真。在工作流顾问中使用 FIL 时,HDL Coder™ 使用加载的设计来创建 HDL 代码。请参阅FPGA-in-the-Loop (HDL Verifier)。

主题

HDL 测试平台

- Using Test Benches With HDL and HLS Code Generation

MATLAB test bench requirements and best practices for HDL and High-Level Synthesis (HLS) code generation. - Specify Test Bench Clock Enable Toggle Rate

Specify test bench clock enable toggle rate. - Verify Code with HDL Test Bench

Simulate the generated HDL design under test (DUT) with test vectors from the test bench using the specified simulation tool. - Test Bench Generation

HDL Coder writes the DUT stimulus and reference data from your MATLAB or Simulink simulation to data files (.dat).

联合仿真

- Set Up for HDL Cosimulation (HDL Verifier)

Overview of cosimulation connectivity options, and HDL simulator set up instructions. - Automatic Verification of Generated HDL Code from MATLAB (HDL Verifier)

Verify generated HDL code using a generated cosimulation script.

FPGA 在环

- FPGA-in-the-Loop Simulation Workflows (HDL Verifier)

Choose between generating a block or System object™, and decide whether to use the FIL Wizard or HDL Workflow Advisor.

故障排除

- Resolve Index Errors During HDL Simulation

Troubleshoot index errors during HDL code simulation.

相关信息

- HDL Cosimulation (HDL Verifier)

- FPGA-in-the-Loop (HDL Verifier)

- FPGA Board Customization