速度与面积优化

通过资源复用、流式传输、流水线、RAM 映射进行改进

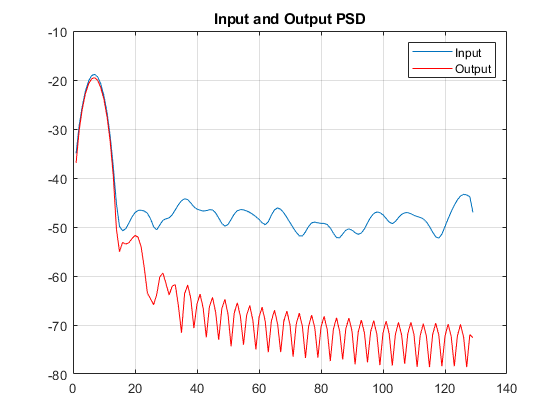

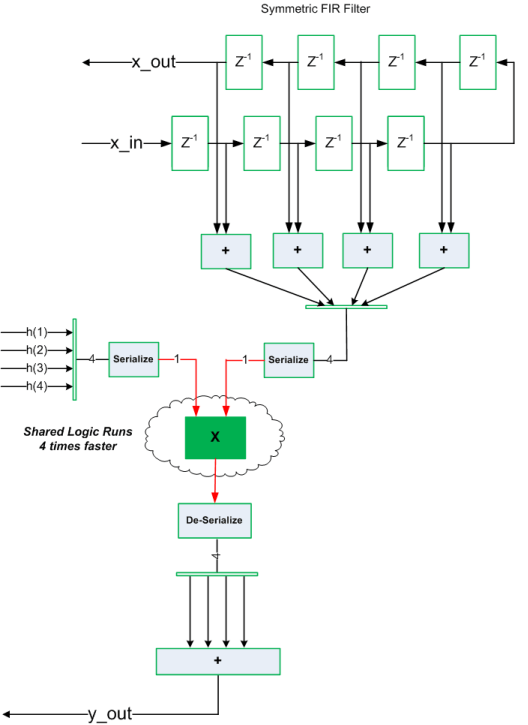

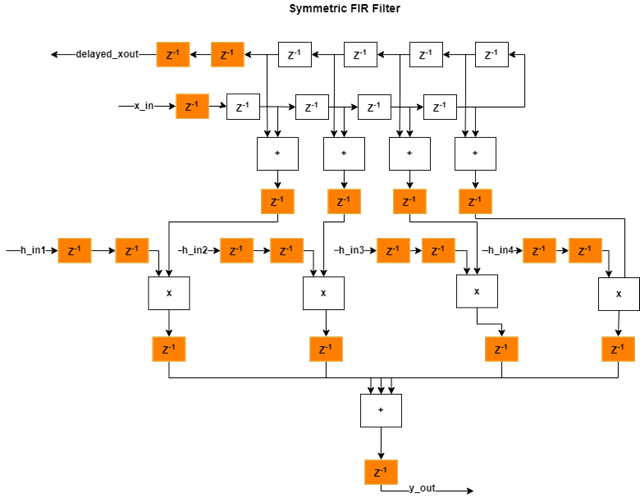

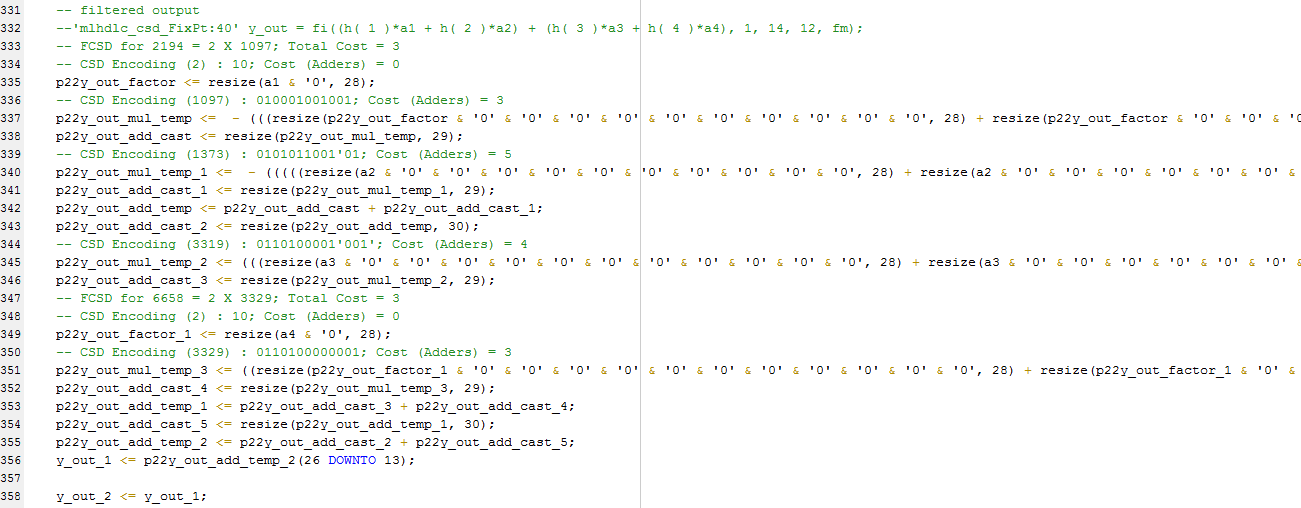

针对目标硬件,通过使用速度和面积优化从 MATLAB® 函数生成满足时序和面积要求的 HDL 代码。面积优化可减少设计的资源使用量。速度优化通过优化关键路径改进目标 FPGA 上的时序,使设计以更高频率运行。要了解 HDL Coder™ 中每种类型的优化的更多信息,请参阅Introduction to Optimizations in HDL Coder。

函数

coder.hdl.loopspec | Unroll or stream loops in generated HDL and High-Level Synthesis (HLS) code |

coder.hdl.pipeline | Insert pipeline registers at output of MATLAB expression |

coder.hdl.ramconfig | Specify RAM mapping configuration for persistent array variables (自 R2023b 起) |

hdl.npufun | Apply neighborhood processing and element-wise operations to incoming image or matrix for frame-to-sample conversion (自 R2022b 起) |

hdl.iteratorfun | Apply iterative operation to an incoming image or matrix for frame-to-sample conversion (自 R2022b 起) |

主题

优化基础知识

- Introduction to Optimizations in HDL Coder

Learn about speed and area optimizations and how to optimize your design. - Specify the Clock Enable Rate

Configure clock enable to run at design base rate or input data rate. - Minimize Clock Enables

Generate code for registers without clock enables. - Constant Multiplier Optimization

What is Constant multiplier optimization and how to specify this optimization.

面积优化

- Apply RAM Mapping to Optimize Area

Map elements to RAM to optimize area on your target hardware. - Manage How HDL Coder Maps RAM

Learn how HDL Coder settings affect RAM mapping. - Map Persistent Arrays and dsp.Delay Objects to RAM

Map persistent arrays anddsp.Delayobjects to RAM on hardware to reduce the area used on your target device. - Map Matrices to ROM

Map matrices to implement ROM in MATLAB and Simulink. - Map Matrices to Block RAMs to Reduce Area

This example shows how to use the RAM mapping optimization in HDL Coder™ to map persistent matrix variables to block RAMs in hardware. - Loop Streaming to Reduce Area

This example shows how to use the design-level loop streaming optimization in HDL Coder™ to optimize area.

速度优化

- Pipelining MATLAB Code

Pipelining helps achieve a higher maximum clock rate by inserting registers at strategic points in the hardware to break the critical path. - Pipeline MATLAB Expressions

Insert registers at output of MATLAB expression. - Optimize MATLAB Loops

Optimize loops for area or speed. - Clock-Rate Pipelining

Pipeline registers insertion at the faster clock-rate instead of the slower data rate.

I/O 优化

- Use Neighborhood, Reduction, and Iterator Patterns with a Frame-Based Model or Function for HDL Code Generation

Generate HDL code from a frame-based design that models neighborhood, reduction, and iterator patterns.