配置并运行 SIL 仿真

运行 SIL 和 PIL 仿真有三种方法。您可以使用:

顶层模型。

Model 模块。

您从子系统中创建的 SIL 和 PIL 模块。

使用顶层模型进行仿真

要配置和运行顶层模型 SIL 或 PIL 仿真,请执行下列步骤:

在 Simulink® 编辑器中,打开您的模型。

在 App 选项卡上,点击 SIL/PIL 管理器。

在模式部分中,选择仅 SIL/PIL 仿真。

在准备部分中,将在测系统设置为顶层模型。

在 SIL/PIL 模式字段中,选择软件在环(SIL) 或处理器在环(PIL)。该选项仅支持 ERT、GRT 或 AUTOSAR 系统目标文件。有关配置信息,请参阅模型配置参数:代码生成和配置 AUTOSAR 代码生成 (AUTOSAR Blockset)。

监控组件信号和状态数据,并比较来自模型和 SIL 或 PIL 仿真的值:

对于您要记录的每个信号:

在 Simulink 编辑器中,选择该信号。

在 SIL/PIL 选项卡上,点击监控信号。从库中,选择以下选项:

记录所选信号

将所选信号设为测试点

信号记录

要记录状态数据,从监控信号库中,选择状态记录。

如果语言配置参数是 C++,代码接口打包是 C++ 类,则在代码映射编辑器中,将信号、状态和内部数据模型元素类别的数据可见性设置为公共。

如果您正在配置 SIL 仿真,请指定可移植字长选项,以解决在 SIL 和 PIL 模式之间切换时字长不匹配的问题。在“配置参数”对话框中,选中启用可移植字长复选框。另请参阅SIL Simulations with Target-Specific Code。

如果需要,配置以下各项:

在运行部分的停止时间字段中,指定仿真时间。

点击运行 SIL/PIL。

仿真结束时,在结果部分中,点击数据检查器以查看仿真结果。

注意

在 Windows® 操作系统上,Windows 防火墙可能会阻止 SIL 或 PIL 仿真。如果您计划将 SIL 或 PIL 仿真作为自动化工作流的一部分运行,请咨询您的 IT 部门以确保仿真未被 Windows 防火墙阻止。

您不能:

在仿真正在运行时关闭模型。要中断仿真,请在命令行窗口中,按 Ctrl+C 键。

在仿真期间更改模型。只要移动模块和信号线不更改模型的行为,就可以移动它们。

您可以使用命令 sim( 运行顶层模型 SIL 或 PIL 仿真。软件支持对值 model)sim 使用 SrcWorkspace 命令选项 'base'。

对于 PIL 仿真,您可以通过连接配置来控制代码在目标环境中编译和执行的方式。

使用 Model 模块进行仿真

要为 SIL 或 PIL 仿真配置 Model 模块,请执行下列步骤:

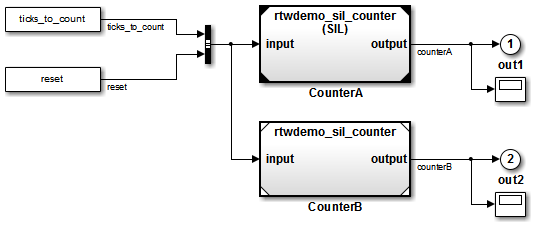

打开您的模型,例如

SILModelBlock:openExample('ecoder/SILPILVerificationExample', ... supportingFile='SILModelBlock.slx')

右键点击您的 Model 模块,例如

Counter A,然后点击“模块参数”按钮 ,这将打开函数的“模块参数”对话框。

,这将打开函数的“模块参数”对话框。从仿真模式下拉列表中,选择所需的模式,例如软件在环(SIL)。

从代码接口下拉列表中,指定要测试的代码,例如模型引用。

点击确定。软件将仿真模式显示为模块标签。

如果您选择顶层模型,软件将显示模块标签

(SIL: Top)。如果您正在配置 SIL 仿真,请指定可移植字长选项,以解决在 SIL 和 PIL 模式之间切换时字长不匹配的问题。在“配置参数”对话框中,选中启用可移植字长复选框。另请参阅SIL Simulations with Target-Specific Code。

在 App 选项卡上,点击 SIL/PIL 管理器。

在模式部分中,选择仅 SIL/PIL 仿真。

在准备部分中,将在测系统设置为 SIL/PIL 模式下的 Model 模块。

在顶层模型模式字段中,选择普通或加速。

如果需要,配置以下各项:

通过为顶层模型配置执行探查,为您的 Model 模块配置代码执行探查。

在运行部分中:

在停止时间字段中,指定仿真时间。

如果您要避免在初始编译后重新编译代码,请点击快速重启。请参阅防止在多个仿真中更改代码。

点击运行 SIL/PIL。

仿真结束时,在结果部分中,点击数据检查器以查看仿真结果。

注意

在 Windows 操作系统上,Windows 防火墙可能会阻止 SIL 或 PIL 仿真。如果您计划将 SIL 或 PIL 仿真作为自动化工作流的一部分运行,请咨询您的 IT 部门以确保仿真未被 Windows 防火墙阻止。

对于 PIL 仿真,您可以通过连接配置来控制代码在目标环境中编译和执行的方式。

使用子系统模块进行仿真

您可以使用以下工作流之一:

已设置 SIL/PIL 管理器的 Simulink Test™ 框架 - 如果您的模型包含子系统,您可以使用 Simulink Test 和 SIL/PIL 管理器对从子系统生成的代码执行单元测试。此工作流测试生成的子系统代码,将其作为从父模型生成的代码的一部分。有关工作流的详细信息,请参阅使用 SIL/PIL 管理器的单元测试子系统代码。

如果此工作流不支持子系统,请使用 SIL 或 PIL 模块工作流作为替代方案。

SIL 或 PIL 模块 - 从子系统创建一个 SIL 或 PIL 模块,然后在提供测试向量或激励输入的环境或测试框架模型中运行该模块。此工作流从子系统中生成并测试新独立代码。有关详细信息,请参阅SIL 或 PIL 模块仿真。

对于 PIL 仿真,您可以通过连接配置来控制代码在目标环境中编译和执行的方式。

SIL 或 PIL 模块仿真

要从子系统创建 SIL 或 PIL 模块并使用此模块测试从子系统生成的代码,请执行下列步骤:

从配置参数 > 代码生成 > 验证 > 高级参数 > 创建模块下拉列表中,选择 SIL 或 PIL。

如果需要,配置代码执行探查。

点击确定。

在模型窗口中,右键点击要仿真的子系统。

要将 Embedded Coder® 选项添加到菜单,请指向选择 App 并点击 Embedded Coder 按钮

。然后,在 Embedded Coder 节中,选择编译此子系统,这将启动子系统编译流程,为生成的子系统代码创建 SIL 或 PIL 模块。

。然后,在 Embedded Coder 节中,选择编译此子系统,这将启动子系统编译流程,为生成的子系统代码创建 SIL 或 PIL 模块。将生成的模块添加到提供测试向量或激励输入的环境或测试框架模型中。

使用环境或测试框架模型运行仿真。

注意

在 Windows 操作系统上,Windows 防火墙可能会阻止 SIL 或 PIL 仿真。如果您计划将 SIL 或 PIL 仿真作为自动化工作流的一部分运行,请咨询您的 IT 部门以确保仿真未被 Windows 防火墙阻止。

如果您执行以下操作之一,则无法创建 SIL 或 PIL 模块:

禁用

CreateSILPILBlock属性。选择代码覆盖率工具。

创建模块呈灰显状态。

配置硬件实现设置

对于 SIL 仿真,您必须配置硬件实现设置,以便为您的开发计算机启用生成的代码编译。这些设置可能不同于针对生产硬件编译模型时使用的硬件实现设置。请使用以下方法之一。

| 方法 | 详细信息 |

|---|---|

| 可移植字长 | 在 SIL 和 PIL 模式之间切换,无需重新生成代码。您可以为开发计算机上的 SIL 仿真和目标平台上的生产部署使用相同的生成源代码文件。 要将模型配置为使用可移植字长,请进行如下设置:

|

当您为指定了可移植字长的模型生成代码时,代码生成器将条件化 #ifdef PORTABLE_WORDSIZES /* PORTABLE_WORDSIZES defined */ … #else /* PORTABLE_WORDSIZES not defined */ … #endif /* PORTABLE_WORDSIZES */ 用于为目标编译代码的模板联编文件不能包含 对于编译代码的模板联编文件和工具链方法,软件仅针对基于主机的编译为编译器指定 有关编译代码的模板联编文件和工具链方法的信息,请参阅配置工具链 (ToolchainInfo) 或模板联编文件编译过程。 | |

假设您的目标使用了开发计算机无法编译的代码。当您从 PIL 模式切换到 SIL 模式并尝试仿真模型时,会发生编译错误。您可以尝试通过将源代码文件添加到编译信息对象

| |

在以下情况之一下,SIL 仿真中执行的生成代码与生产硬件上执行的生成代码之间的数值结果可能不同:

| |

| 测试硬件 | 仅当您要解决可移植字长的限制时,才使用这种方法。 进行如下设置:

|

| 生产硬件 | 仅当生产硬件设置与您的开发计算机架构匹配时,才使用这种方法。 进行如下设置:

|

有关测试和生产目标的信息,请参阅 Simulink Coder 中的 配置运行时环境选项。

组件的日志信号

SIL 和 PIL 组件输出可用于观测值和与其他仿真模式输出进行比较。如果您要检查内部信号,可以启用顶层模型或 Model 模块 SIL 或 PIL 的内部信号记录。使用信号记录,您可以:

在 SIL/PIL 仿真期间收集信号记录输出,例如

logsout。记录 SIL/PIL 组件的内部信号和根级输出。

使用 Simulink 信号记录选择器管理 SIL/PIL 信号记录设置。

使用仿真数据检查器可以:

观测普通、SIL 和 PIL 仿真期间的流式传输信号。

比较普通、SIL 和 PIL 仿真的记录信号。

在 SIL 或 PIL 仿真期间,要将信号记录到 MATLAB 工作区并将信号流式传输到仿真数据检查器,请执行下列步骤:

对于您要监控的每个信号:

在 Simulink 编辑器中,选择该信号。

在 SIL/PIL 选项卡上,点击监控信号。从库中,选择以下选项:

记录所选信号

将所选信号设为测试点

信号记录

如果语言配置参数是 C++,代码接口打包是 C++ 类,则在代码映射编辑器中,将信号、状态和内部数据模型元素类别的数据可见性设置为公共。

您可以使用其他方法来检查 SIL 或 PIL 组件的内部信号:

手动将信号传送到顶层。

使用全局数据存储来访问内部信号:

在组件内部,将 Data Store Write 模块连接到所需的信号。

在组件外部,使用 Data Store Read 模块访问信号值。

使用 MAT 文件记录。请注意:

MAT 文件记录不支持信号记录。如果启用信号记录,则会生成

logsout,但它不会存储在 MAT 文件中。对于 PIL,目标环境必须支持 MAT 文件记录。

有关详细信息,请参阅:

防止在多个仿真中更改代码

当您要在如下情形下运行多个 SIL 或 PIL 仿真,可配置使用 Model 模块 SIL/PIL 或 SIL/PIL 模块并采用快速重启模式:

使用变化的测试向量(参数集和输入数据)。

使用未更改的生成代码,也就是说,在初始编译后,没有任何仿真重新生成或重新编译代码。例如,您要避免初始值更改可能触发的增量代码生成。

对于 Model 模块 SIL/PIL,您也可以创建一个受保护模型并生成源代码或二进制代码。然后,将受保护模型插入到您的测试框架模型中。使用这种方法,您可以验证顶层模型代码(使用独立代码接口)或模型引用代码。

对于运行 Model 模块 SIL/PIL 的替代方法,下表总结了初始编译后的代码生成行为。

| SIL 和 PIL 方法 | 初始编译后的代码生成行为 |

|---|---|

| 受保护模型的二进制代码。 |

|

| 受保护模型的源代码。 | 除了特征 2 之外,您观测到相同的行为。在这种情况下,会运行组件代码联编文件。组件代码会重新编译并链接以生成新目标代码。 |

有关详细信息,请参阅保护模型以隐藏内容。

加速测试

如果您的模型在 SIL/PIL 模式下有 SIL/PIL 模块或 Model 模块,您可以通过以下方式加速 SIL/PIL 测试:

注意

SIL 和 PIL 仿真模式不是为了减少模型仿真时间而设计的。如果您要加快模型的仿真速度,请使用快速加速模式。有关详细信息,请参阅 What Is Acceleration?。

使用函数调用进行仿真

当您要执行以下操作时,请使用 Simulink Function 模块:

生成对外部代码(例如驱动或现有代码)进行函数调用的代码。

提供其行为类似于普通、SIL 或 PIL 仿真中的外部代码的子系统。

Configure Calls to AUTOSAR NVRAM Manager Service (AUTOSAR Blockset)中的示例说明如何配置从 AUTOSAR 软件组件对 Basic Software (BSW) NVRAM Manager (NvM) 服务接口的客户端进行调用。在仿真中,Simulink 通过 Simulink Function 和预配置的 Function Caller 模块实现 BSW NvM 调用。对于最终系统,请将函数调用桩件与在 AUTOSAR 运行时环境 (RTE) 中运行的外部 BSW 函数代码链接起来。

有关详细信息,请参阅Simulink Function Blocks and Code Generation。

另请参阅

主题

- SIL 和 PIL 仿真

- 选择 SIL 或 PIL 方法

- 用 SIL 和 PIL 仿真测试生成的代码

- Debug Generated Code During SIL or PIL Simulation

- View SIL and PIL Files in Code Generation Report

- SIL/PIL Manager Verification Workflow

- 以编程方式运行仿真

- Simulation Mode Override Behavior in Model Reference Hierarchy

- SIL and PIL Limitations

- Configure Code Coverage with Third-Party Tool

- Create Execution-Time Profile for Generated Code