多处理器架构建模

设计、评估和实现多处理器架构建模

对算法进行分区,以通过处理器间数据通信 (IPC) 及协处理器(控制律加速器)模块实现多核执行。通过处理器在环 (PIL) 仿真,您可以在开发计算机上交叉编译源代码,然后将目标代码下载并运行在硬件板上的处理器中。

使用硬件映射工具将模型中的任务和外设映射到硬件板配置。

模块

主题

处理器在环 (PIL) 仿真

- PIL 仿真

Texas Instruments硬件板的处理器在环 (PIL) 仿真技术。

多处理器建模

- Use C2000 blocks with Multiprocessor Modeling

Use multiprocessor modeling pass-though block simulation with C2000™ Microcontroller Blockset blocks. - Interprocess Data Communication via Dedicated Hardware Peripheral

Data communication methods between two or more processes within a single processor or across multiple connected processors. - Modeling and Code Generation Using Hardware Interrupt

Model and generate code using Hardware Interrupt block. For multiprocessor modeling use Task Manager block and Hardware Mapping tool. - Streaming Task Profiling

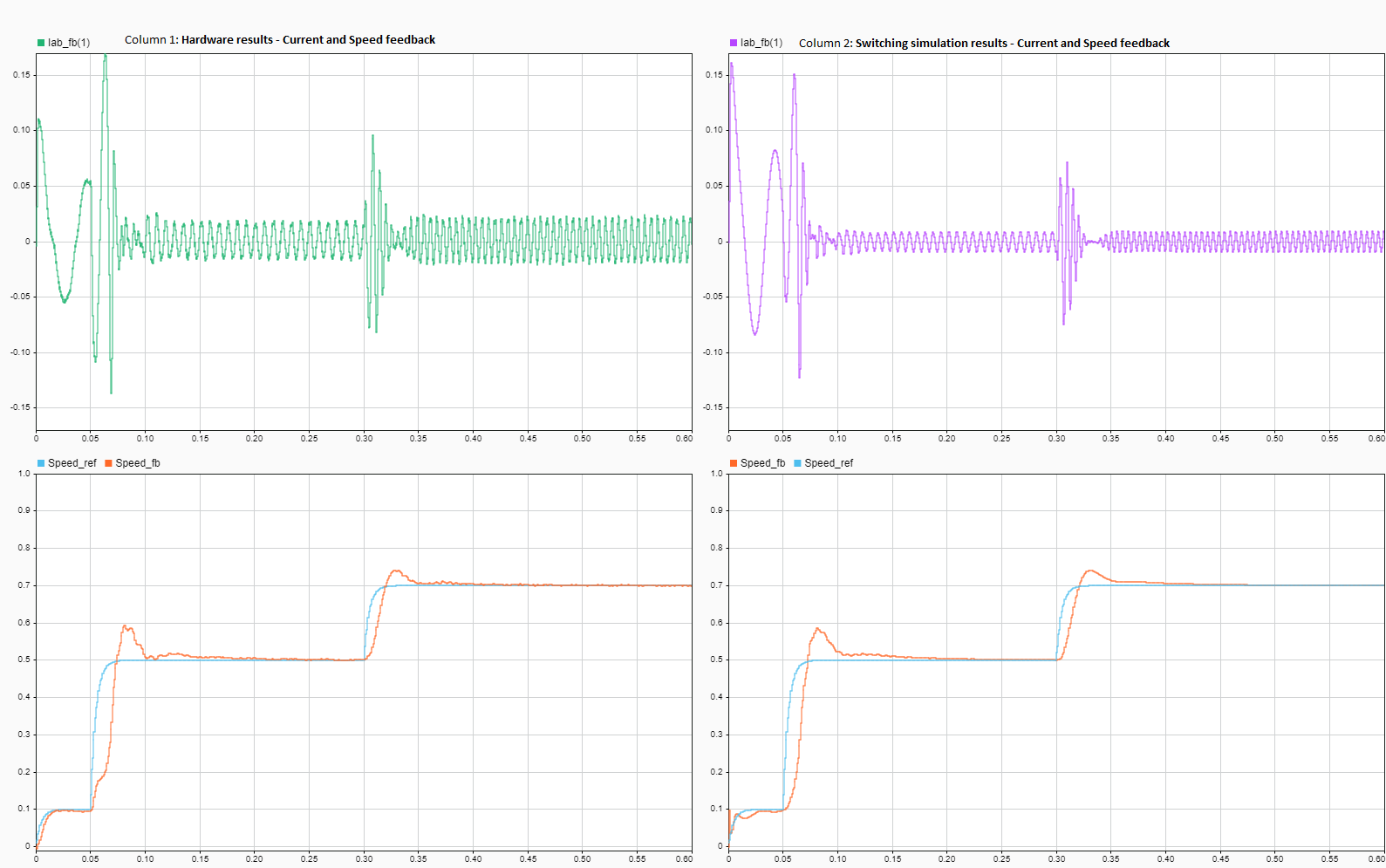

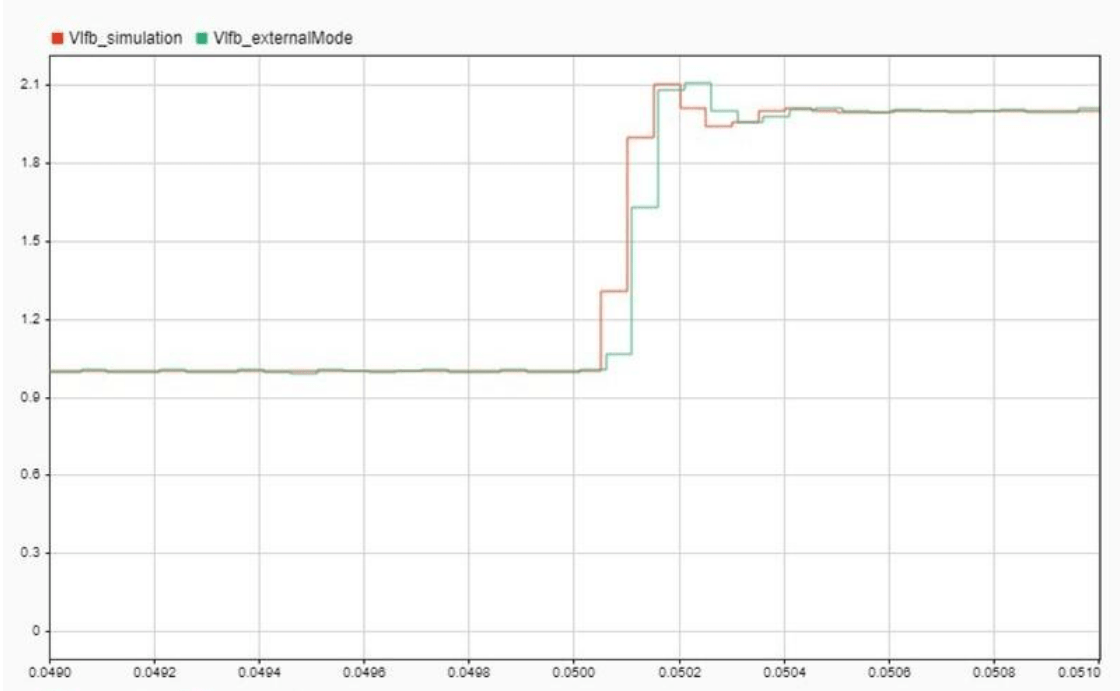

Use the streaming task profiler to measure tasks on the TI C2000 processor. - Run Multiprocessor Models in External Mode

Run a multiprocessor SoC model in external mode running on separate processors on the hardware board. - Modeling Control Law Accelerator (CLA) Using Model Reference

Use the control law accelerator (CLA) co-processor in C2000 MCU models. - Using ARM Cortex-M Coprocessor

Use the ARM® Cortex®-M coprocessor in C2000 MCU models. - Communication Between Cores Using IPC Blocks

Use the IPC blocks to communicate between cores in F2837xD and F2838x processors on the TI C2000 processor.

疑难解答

Solve the problems while using SoC Builder for Multiprocessor Architecture Modeling.