自定义 IP 核生成

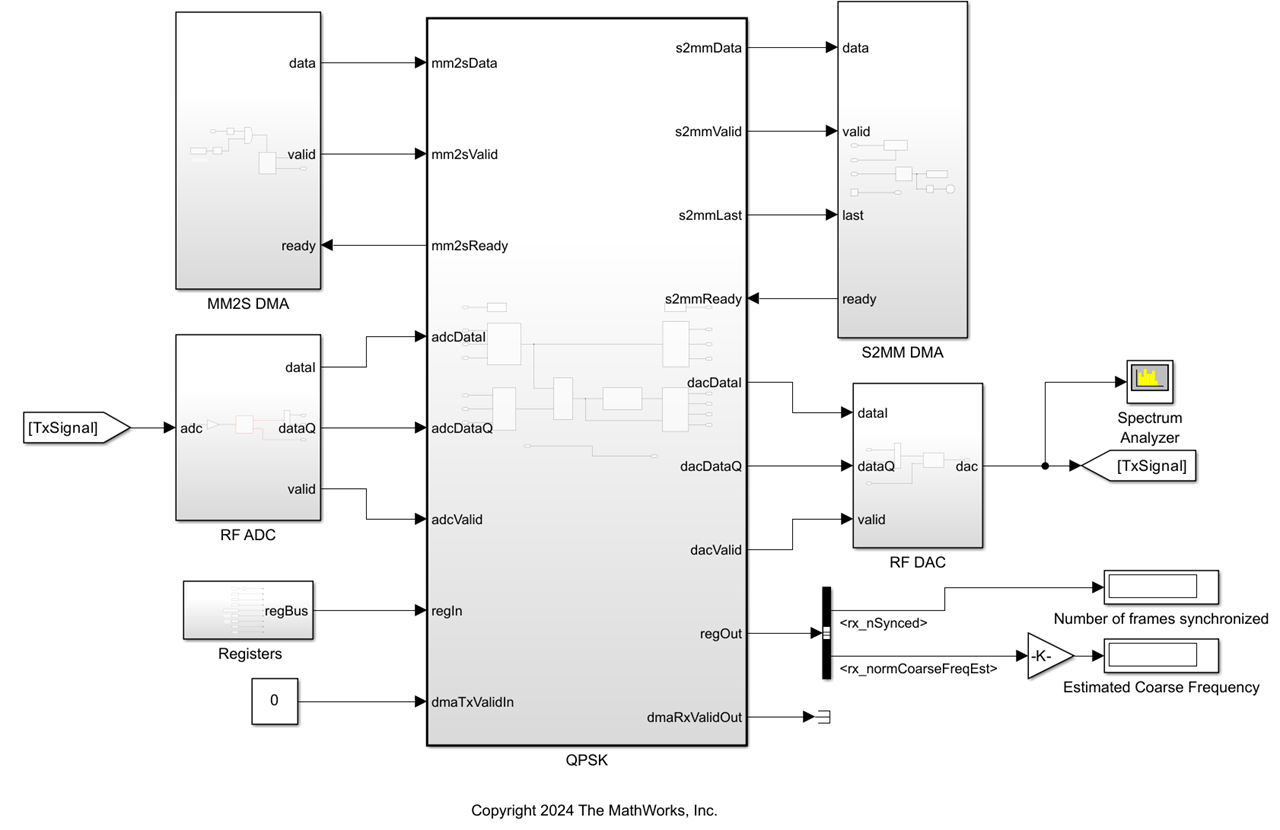

HDL Coder™ 可以生成可部署到设备上的自定义 HDL IP 核。您可以将生成的 IP 核集成到默认系统参考设计中,或集成到为板注册的自定义参考设计中。

主题

- Generate an IP Core for AMD SoC Devices from MATLAB

IP core generation for AMD® SoC Devices from MATLAB®.

- Generate an IP Core for AMD SoC Devices from Simulink

IP core generation for AMD SoC Devices from Simulink®.

- IP Core Generation Workflow for AMD FPGA Boards

Learn how to use the IP Core Generation workflow with standalone FPGA devices and embed the IP core into the reference design.

- Custom IP Core Generation

Generate a custom IP core from a model or algorithm using the HDL Workflow Advisor.

- Custom IP Core Report

You generate an HTML custom IP core report by default when you generate a custom IP core.

- IP Caching for Faster Reference Design Synthesis

Use IP caching to speed up reference design synthesis time by using an out-of-context workflow.

疑难解答

Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.