UVM Generation

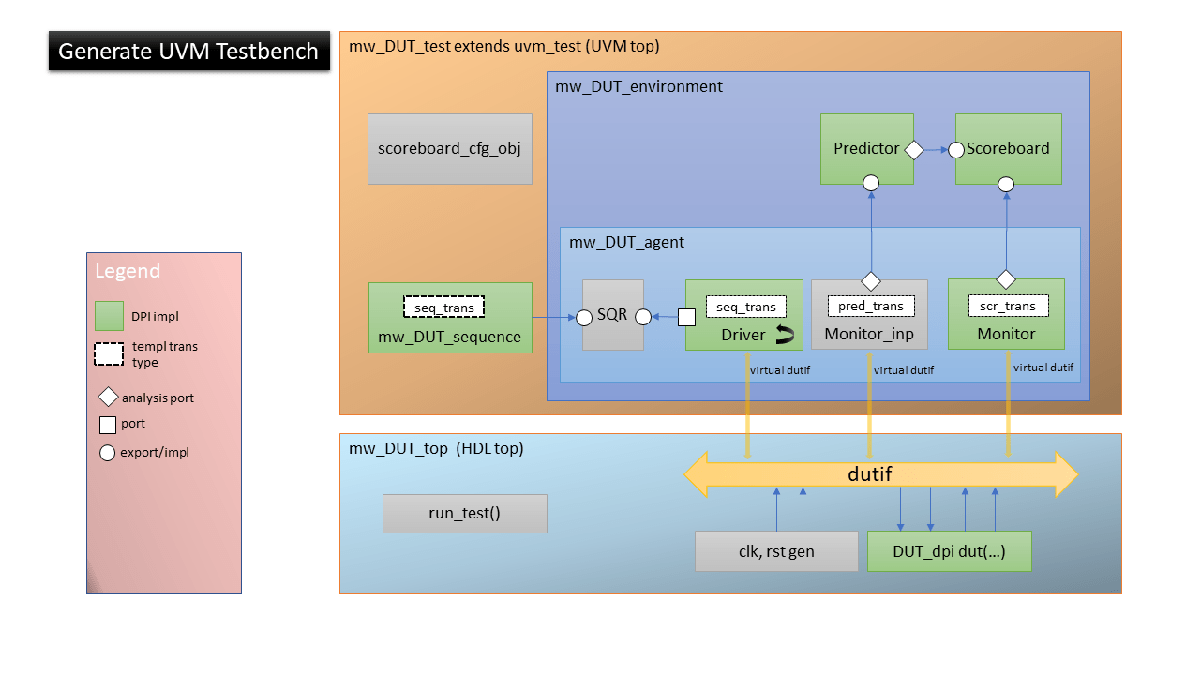

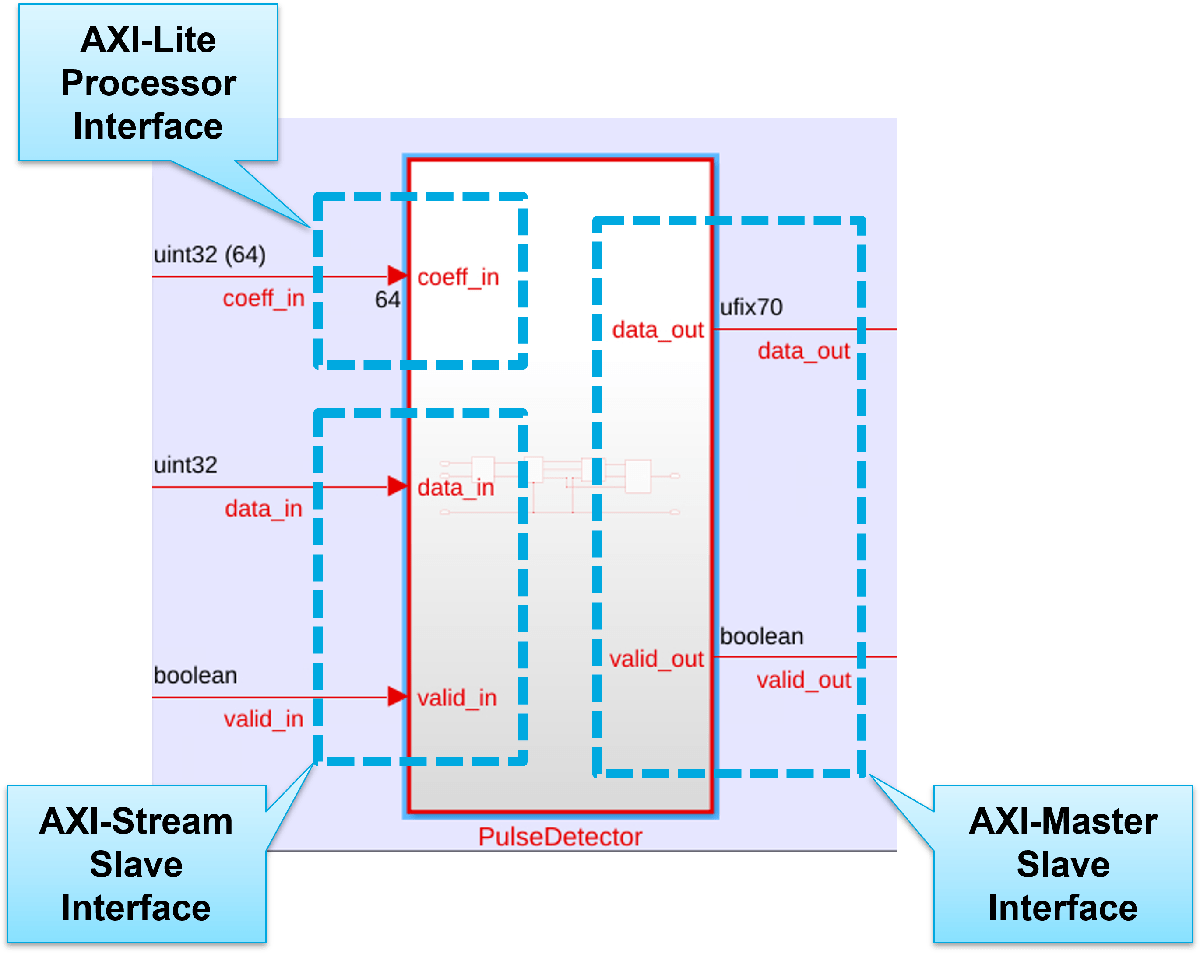

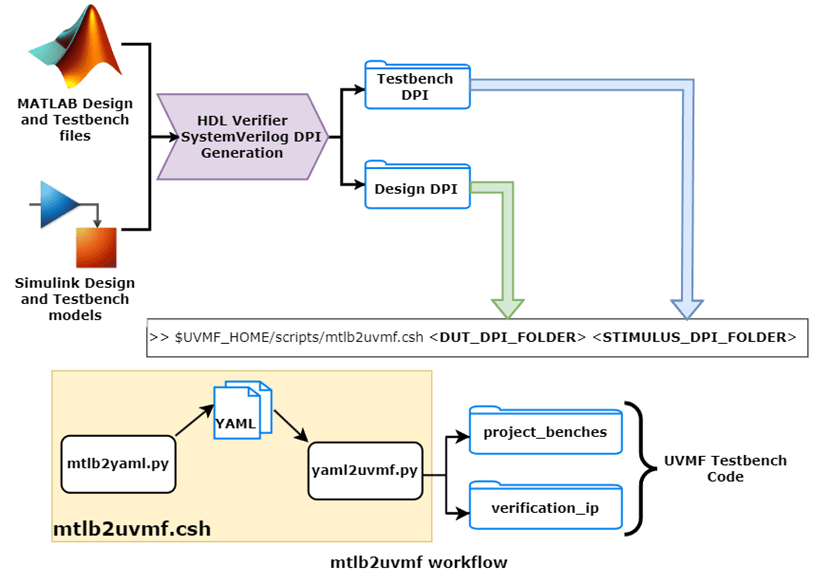

Generate Universal Verification Methodology (UVM) test components and a behavioral design under test (DUT) from a Simulink model. You can use the generated components in two ways.

Generate a UVM top model with a testbench and a behavioral (DUT). Use the generated UVM top module as a test environment, and replace the generated behavioral DUT with your own simulation model.

Generate UVM test components, and integrate them into your existing UVM environment.

To use this functionality, download and install the ASIC Testbench for HDL Verifier add-on. This feature also requires Simulink Coder™.

Not all UVM generation functionalities are available in MATLAB Online™.

Functions

Blocks

| Sequence Feedback | Connect between scoreboard and sequence in UVM testbench model (Since R2023a) |

Objects

uvmcodegen.uvmconfig | UVM configuration object |

svdpiConfiguration | Configure workflows for UVM and SystemVerilog component generation from MATLAB (Since R2023a) |

uvmfTestBenchConfiguration | Configure YAML generation from DPI component generation and its integration with UVMF (Since R2024a) |

Model Settings

Topics

UVM Generation from Simulink

- UVM Component Generation Overview

Generate a Universal Verification Methodology (UVM) environment from a Simulink model. - Customize Generated UVM Code

Customize file banners and HDL simulation timescale when generating a UVM testbench. - Generate SystemVerilog Assertions and Functional Coverage

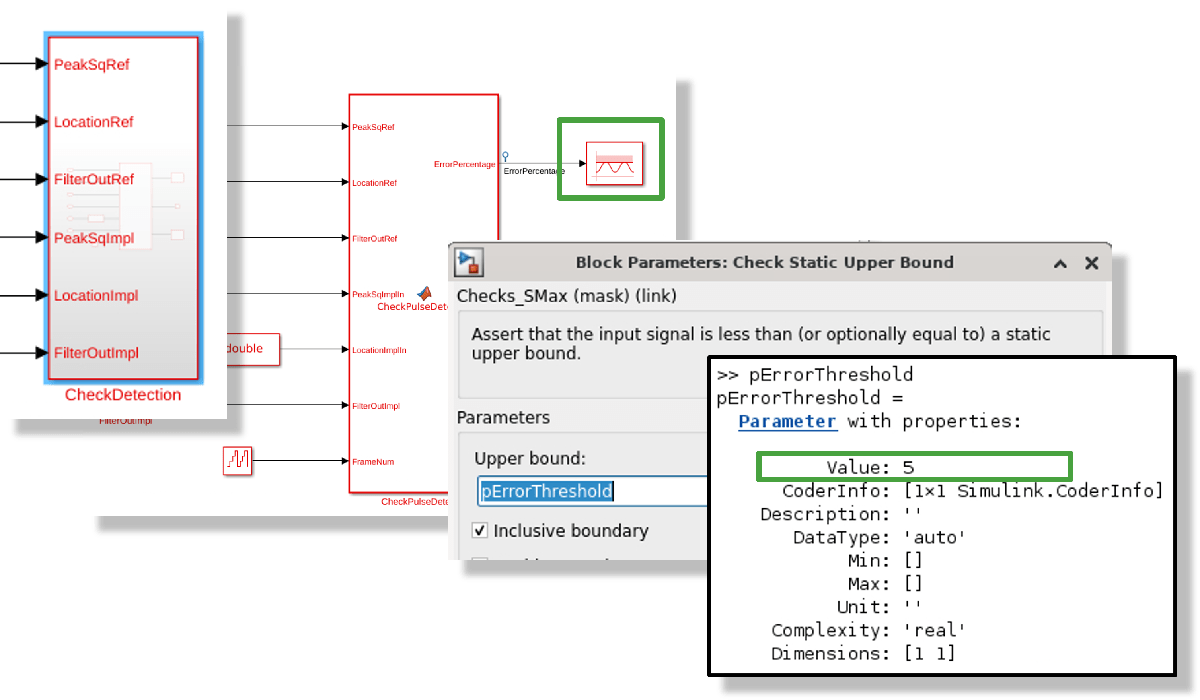

Generate SystemVerilog immediate assertions fromverifystatements and model verification blocks, and collect functional coverage information (requires Simulink Test™ license). - Use Tunable Parameters to Generalize UVM Simulation

Generate UVM parameters from Simulink tunable parameters. - Tunable Parameters in Sequence Subsystem

Generate random constraint parameters in UVM sequence from Simulink tunable parameters. - Tunable Parameters in Scoreboard Subsystem

Generate random constraint parameters in UVM scoreboard from Simulink tunable parameters. - Generate Individual UVM Component from Simulink

Generate a Universal Verification Methodology (UVM) component from a Simulink model.

UVM Generation from MATLAB

- SystemVerilog and UVM Templates

Generate customizable SystemVerilog modules and UVM components from MATLAB using templates. - Custom Template Language Syntax

Template variable definition and usage. - Generate Cross-Platform UVM Components

Generate the UVM components for a Linux® operating system from your Windows® host machine.

UVM Framework

- Prepare DUT for UVM Framework Generation

DUT requirements for UVMF generation.